如何获取下降沿逻辑代码

获取下降沿逻辑代码的关键在于检测信号由高电平向低电平的瞬时变化,本质是比较前后状态并识别边沿触发。常见实现方式包括硬件中断配置、软件轮询判断、硬件描述语言负边沿触发以及操作系统级GPIO监听。相比软件方式,硬件下降沿检测具有更高实时性和稳定性。在实际项目中还需结合防抖处理与系统架构优化,以提升可靠性与响应效率。掌握多平台实现方法,有助于构建高性能数字控制系统。

William Gu

William Gu- 2026-04-09

代码中如何避免亚稳态

在数字电路与嵌入式系统设计中,亚稳态是由于异步信号或跨时钟域采样违反建立保持时间而产生的物理现象,无法彻底消除,但可以通过工程手段有效控制。常见方法包括双触发器同步、多位数据使用握手机制或异步缓冲结构、采用Gray码减少位翻转,以及结合严格的时序约束与CDC分析工具进行验证。代码层面应避免直接使用异步信号驱动状态机或组合逻辑,并统一封装同步模块。随着系统频率不断提升,亚稳态防护将更加依赖架构级规划与可靠性设计能力。通过系统化设计与验证,可以将亚稳态风险降低到满足工程可靠性的水平。

Joshua Lee

Joshua Lee- 2026-04-08

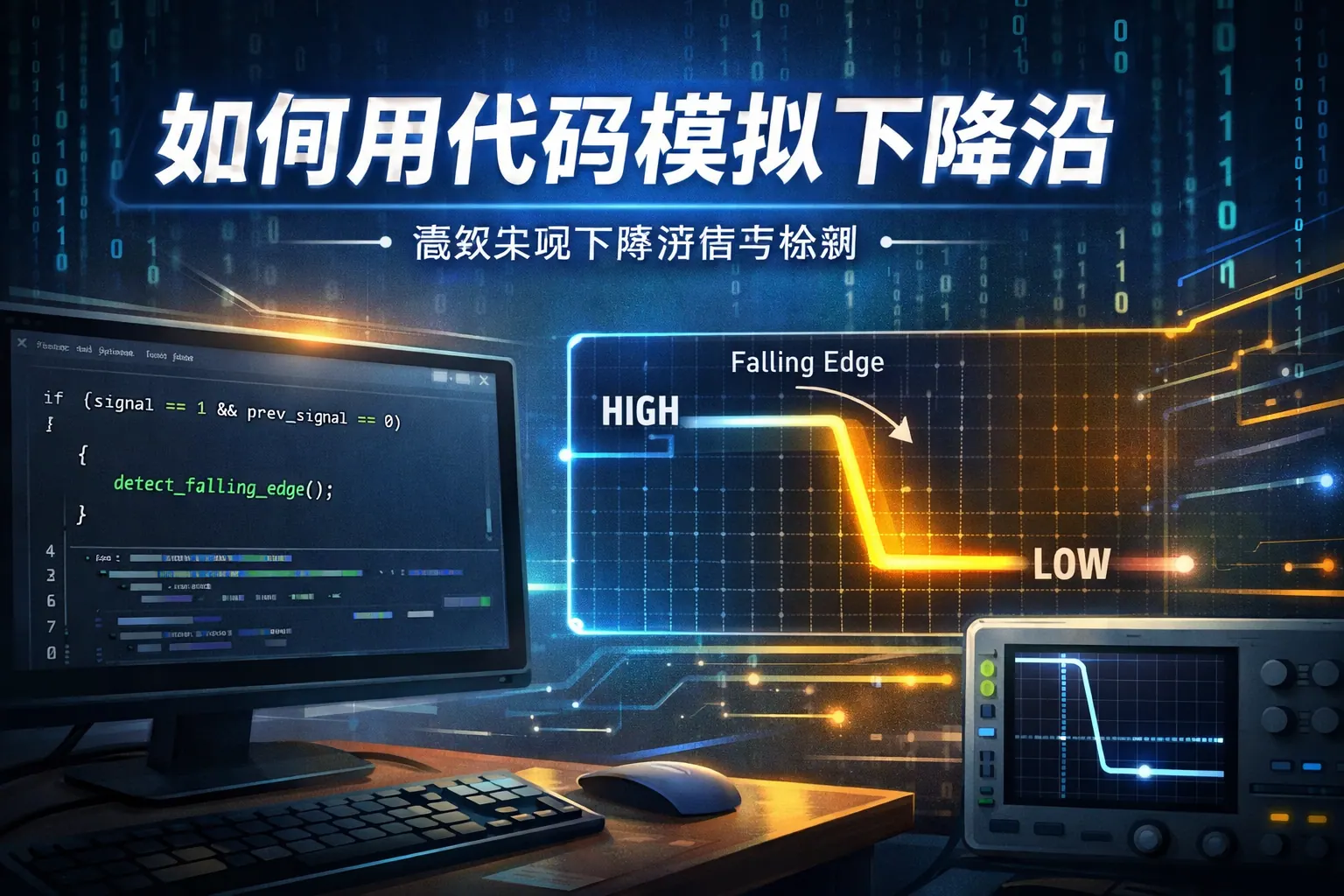

如何用代码模拟下降沿

代码模拟下降沿的核心是通过记录并比较前后两次信号状态,在检测到由高电平变为低电平的瞬间触发逻辑。无论是在单片机轮询、中断机制,还是在FPGA硬件描述语言中,本质都是实现边沿检测算法。实际应用中需结合中断方式、去抖处理与采样频率优化,以提升检测精度和系统稳定性。未来下降沿检测将与智能信号处理深度融合,成为数字系统设计的重要组成部分。

William Gu

William Gu- 2026-04-07

如何调用分频的代码

调用分频代码的关键在于理解分频原理、准确计算分频系数,并根据不同平台选择合适实现方式。在单片机中通常通过定时器初始化与中断调用完成分频,在FPGA中则通过计数器模块实例化实现。实际开发中应优先采用硬件分频以提高精度与稳定性,同时注意时钟源确认、计数器位宽计算及同步设计规范。掌握这些核心方法,可以在嵌入式与数字系统开发中高效实现稳定可靠的频率控制。

Rhett Bai

Rhett Bai- 2026-04-07

如何用代码表示下降沿

下降沿是数字信号从高电平跳变为低电平的瞬间,用代码表示本质是比较当前与历史状态,判断是否发生“1→0”变化。实现方式包括轮询检测、外部中断、定时器捕获、PLC触发器及FPGA逻辑等。不同平台实现机制不同,但核心逻辑一致。实际工程中需注意抖动、实时性和并发问题,并根据系统性能选择合适方案。随着嵌入式与工业控制发展,下降沿检测正向高精度和事件驱动架构演进。

Elara

Elara- 2026-04-03

代码如何转变成信号格式

代码之所以能够变成计算机可执行的信号,本质在于它先被编译为机器指令,再编码为二进制数据,最终通过晶体管对电压高低的响应转化为电信号在电路中传输与执行。整个过程涵盖编译器转换、指令集编码、数字电路开关、时钟同步以及物理信号传播等多个层级,是从抽象逻辑到物理状态变化的连续映射。理解这一链路,有助于深入掌握计算机底层原理与性能优化机制。

Joshua Lee

Joshua Lee- 2026-04-03

代码如何表示上升沿

代码表示上升沿的核心方法是比较信号前后状态,当检测到由低电平变为高电平时触发逻辑。不同环境下可通过软件轮询、硬件中断或时序关键字实现,上升沿检测广泛应用于嵌入式系统、操作系统与数字电路设计。理解其原理、实现方式与防抖机制,是构建稳定实时系统的重要基础,未来也将向事件驱动与硬件加速方向发展。

Elara

Elara- 2026-04-01