其实每年英伟达的GTC开发者大会报道,电子工程专辑的解读都略有点格格不入。因为英伟达虽说是造GPU的,但GTC的大量篇幅都是在谈软件、库、中间件、应用开发——在我们看来,GTC更像是给计算机科学(CS)那帮人看的,而不是电子工程(EE)。EE可以说是CS实现的下层和基础。

但这其实是个悖论,也就是即便再底层的技术,都越来越离不开CS。比如说我们提到“AI”,一般说的是某种很上层的技术——它依托于AI芯片,重头戏实则在网络模型和应用开发;但另一方面,AI技术又在反哺芯片设计。所以说到底,EE和CS都是相辅相成的。而且今年终于有了一个和半导体制造最相关的软件发布。

即英伟达专为计算光刻(computational lithography)发布了软件库,名为cuLitho。其实英伟达针对任何领域发布一些中间件和库,属于这家公司的日常,生物制药、化学、气候预测、量子计算等等,都不新鲜。但今年针对cuLitho,虽然黄仁勋在主题演讲中只说了大约不到5分钟,但英伟达特别面向媒体就cuLitho做了个单独的pre-briefing——在GTC期间也有专门针对这个库的session。这表明英伟达本身应该还是非常看重cuLitho的。

恰好借着这个机会,我们也能管中一窥地了解计算光刻。

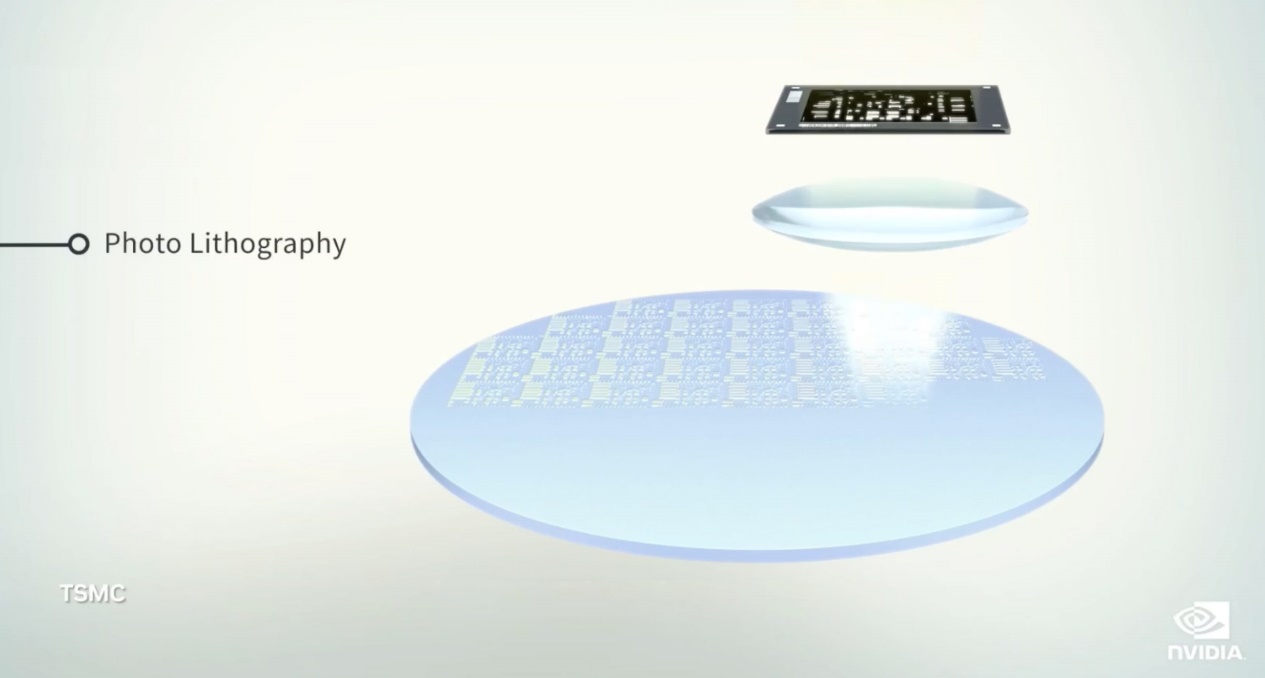

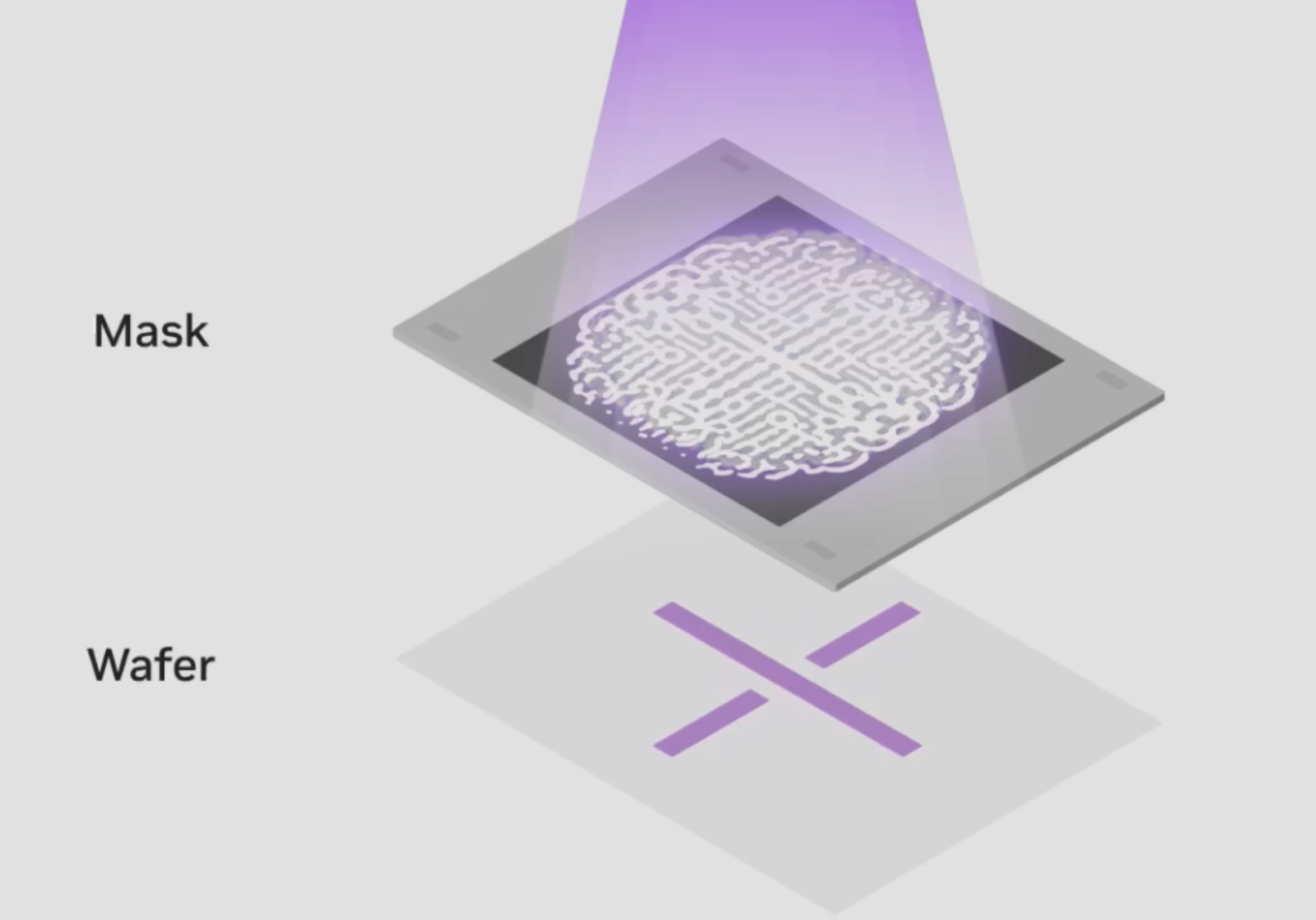

对于光刻其实不必花太多笔墨做介绍了。这是芯片制造过程中最重要的一个步骤,就像是用“光刀”在晶圆上“雕刻”一样。“雕刻”当然是要“刻”出特定的图案的。这个图案首先要呈现在光掩膜(photomask)上。掩膜板就像是漏字板,激光一照,通过镜头,“漏字板”上的图案也就落到了硅片上,如下图。

晶体管、器件、互联线路都需要经过这样的光刻步骤。实操当然比这三两句话的形容要复杂得多,比如现在的芯片上上下下那么多层,不同的层就需要不同的光刻和掩膜板;而且某些层如果器件间距很小,就可能需要多次光刻。

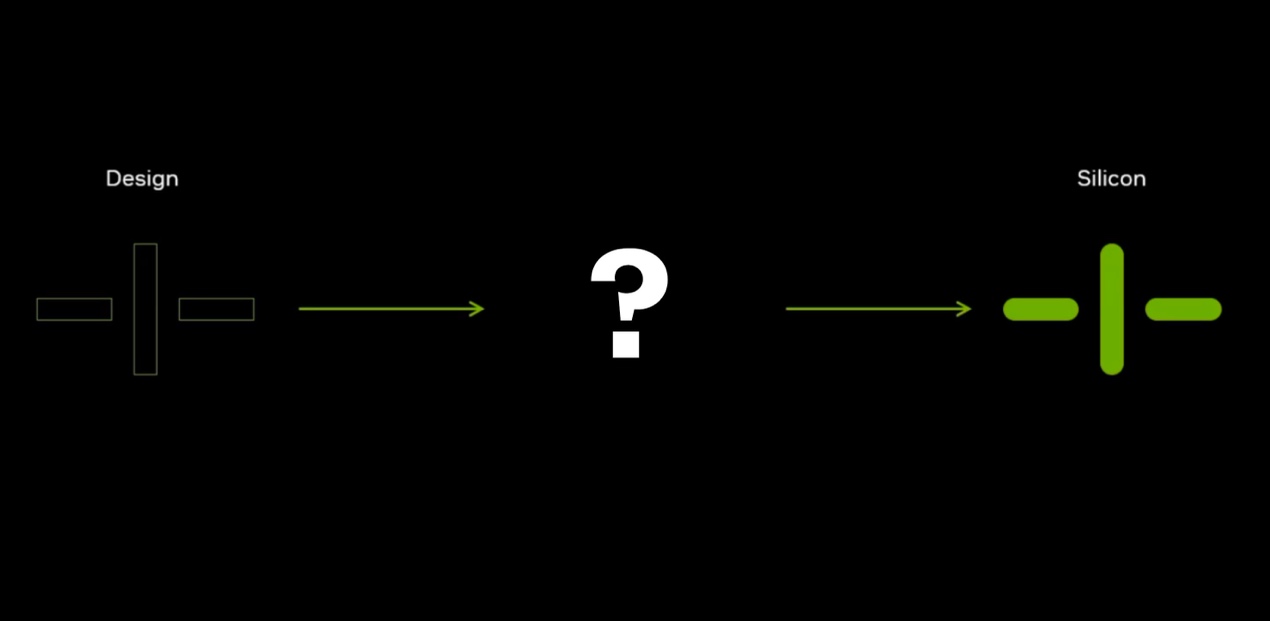

这里面还有个很反常识的事,就是在我们的认知里,比如要光刻上面这个图案,几个长方形——那么掩膜板要做成图中左边镂空的样子,则光源照射以后,落在硅片上就变成了图中右侧的样子。但实际情况却并不是这样的。光掩膜其实要做成下面这样:

这掩膜板复杂成这样,是不是挺反直觉的?光一照,刻到晶圆上会变成下面这样?英伟达先进技术副总裁Vivek Singh解释说,半导体发展的过去几十年,晶体管和互联间距变得越来越小——原本一切发展都还算顺利。但“大概30年前,晶体管的尺寸变得比(光刻机所用的)激光波长还要小,于是衍射效应就产生了,晶体管成像就会变得模糊”。

对光学或者摄影有了解的同学,对衍射效应这个词应该不会陌生。对于相机而言,当光圈小到某种程度以后,照片受到衍射效应的影响就会显著增大,导致画面解析力的大幅下降;实际上,超高像素(或小像素)也受制于衍射效应。这一点体现在比相机精密很多的光刻机上,也是类似的。Vivek就把光刻机称作是“fancy camera”。

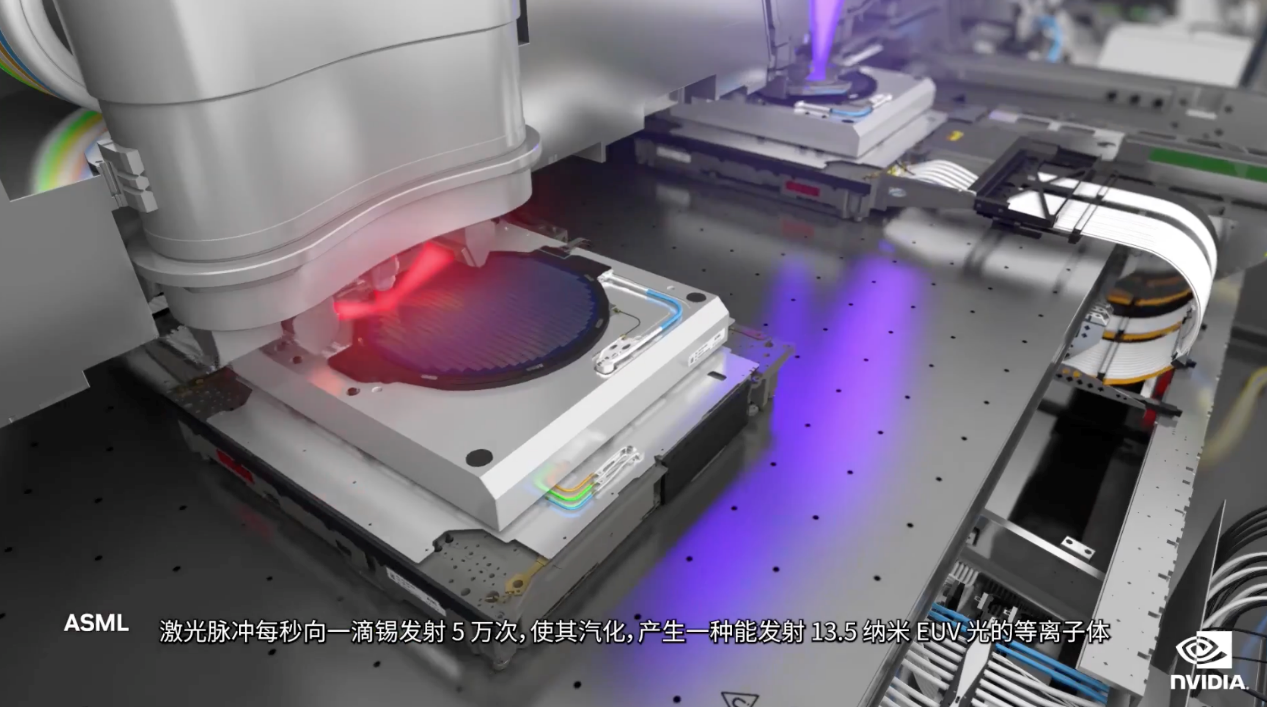

当然,我们知道光刻机所用光源也有过几次大的迭代,到现在谈论非常多的就是DUV和EUV。尤其EUV极紫外光刻是波长显著变小的一代光源了。不过即便是昂贵的EUV,其波长与器件间距之间的差异,也变得比过去更小。换句话说,光刻图案未来将一步步走向模糊——或者说没有很高的保真度。

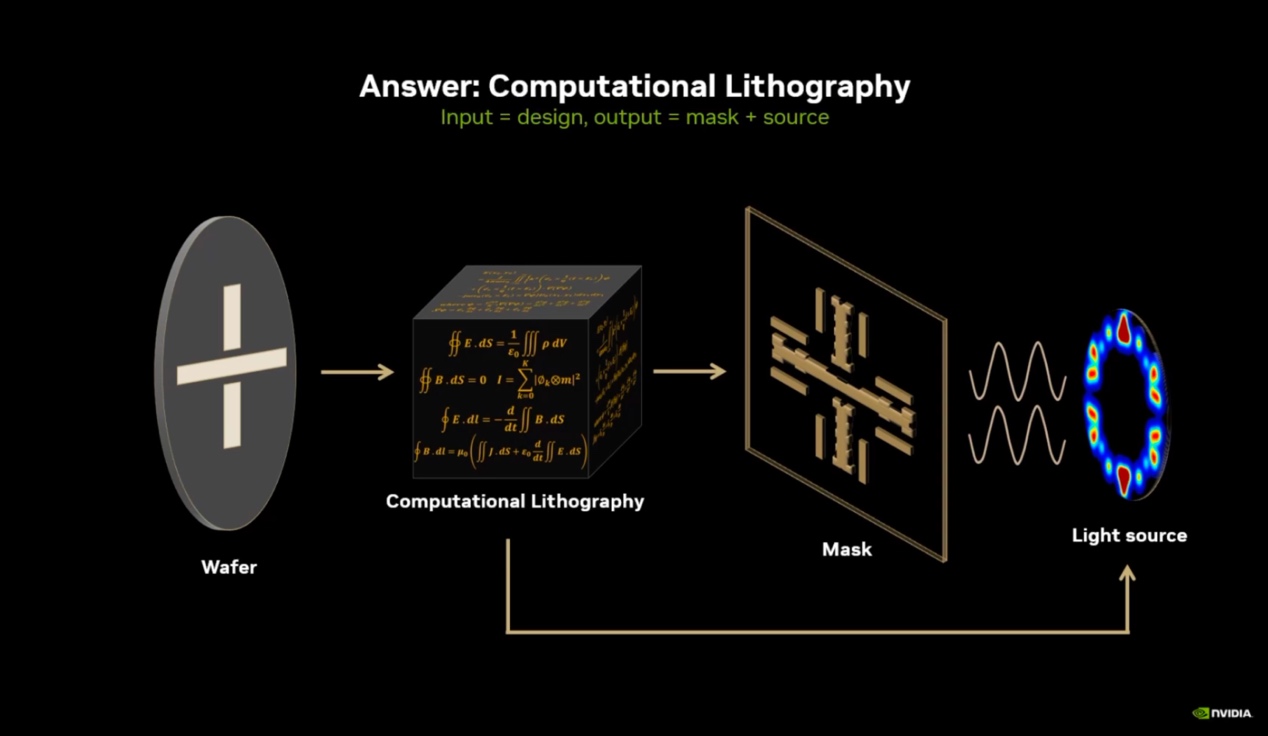

这就是计算光刻切入的契机——至少藉由计算光刻要缓解这方面的像差,对于芯片制造产生的不良影响。

此前我们探访ASML中国,就听ASML聊起过计算光刻。计算光刻是ASML的“铁三角”业务之一。ASML告诉我们,计算光刻是通过软件,对整个光刻过程来做建模和仿真,对工艺流程做优化;比如说形貌优化、掩膜板修正等。举个例子,比如ASML有个“自由形状照明(freeform illumination)”,就是通过改变照明形态来提高成像的解析力。

这就是上面那张图,光掩膜看起来如此奇怪的原因。即为消除光刻过程中,小尺寸器件“模糊”的问题,就需要对光路上的组成部分做修改。这就好像:在要求得到某个结果(这一例也就是几个长方形的图案)时,算出光源、光掩膜需要做哪些调整。这个过程就是计算光刻。

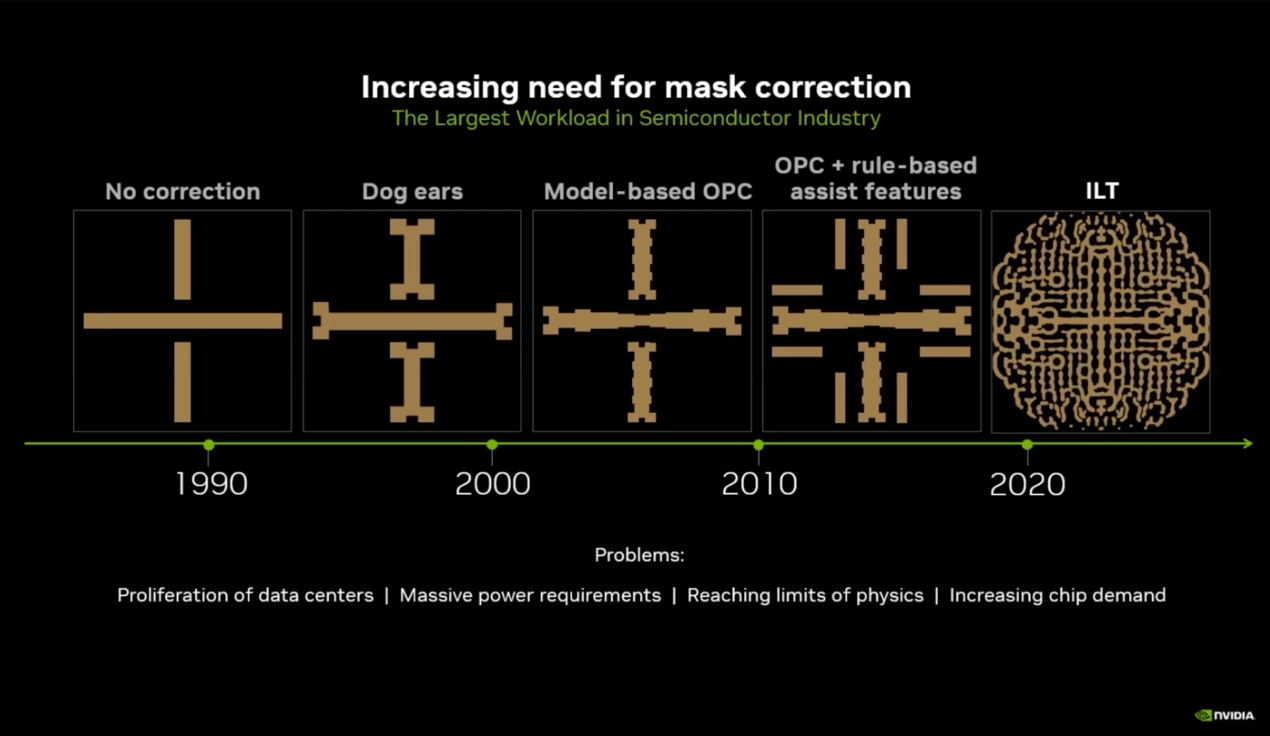

上图中英伟达呈现了上世纪90年代,光掩膜和光刻成像原本的所见即所得,到后续“dog ears”、基于模型的OPC(光学临近效应修正),以及RBAF(基于规则的辅助特征)加上OPC。最后得到恐怖如最右边这个样貌的掩膜——就为了在晶圆上得到一个交叉图案。这里的ILT(Inverse Lithography Technology,反演光刻技术)和前面的OPC都属于计算光刻的组成部分。

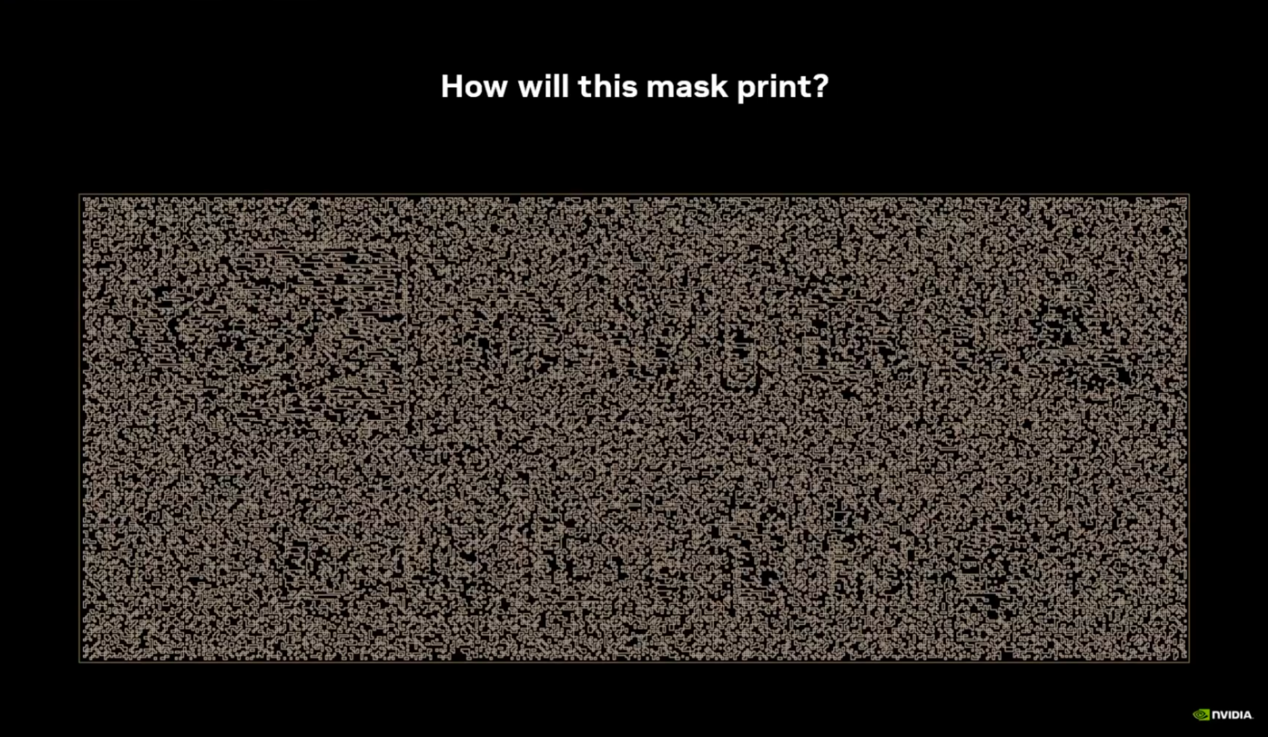

真正反直觉的其实是下面这张图就是以掩膜板如此图案(叫做chromeless phase-shifted mask?),最终光刻出来的是NVIDIA cuLitho字样。是不是感觉特别不可思议?据说是用ASML的光刻机搞出来的。

当然,上面这番解释给出的条件还是不够充分。但可以明确的是,随着晶体管和互联线宽的持续微缩,掩膜板的复杂度可能会越来越高。Vivek说,foundry厂所需的数据中心规模扩张速度,会比摩尔定律本身的发展速度还要快;最终就是没有足够多的算力来解决问题。

“按照过去15年的趋势,如果某个foundry厂现有3座数据中心,那么未来10年内就需要100座这样的数据中心。”Vivek说,“功耗方面,45兆瓦(MegaWatt)或许还行,但如果是45千兆瓦(GigaWatt),问题就比较大了。英伟达对此给出的回答是cuLitho。”

其实就英伟达的角度来看,这件事和数据中心发展的本质是类似的。上个月国际电子商情封面故事是谈GPU的。其中提到2030年数据中心服务器的价值占比中,加速器将超过CPU——而加速器的主要类型就是GPU。我们对于foundry厂用作计算光刻的数据中心不怎么了解。不过Vivek在答记者问中说,传统foundry厂的数据中心是以CPU为主的。

Vivek说,OPC的一部分工作就是成像(image formation),这项工作内包含了大量矩阵乘运算——这种运算很适用于GPU加速。这样一来也就大大加速了OPC的整体工作过程。说到底,计算光刻也是GPU通用计算加速的某一个应用方向。

cuLitho作为面向这一领域的加速库,由英伟达发布就很好理解了。英伟达在宣传中说,用Hopper架构的GPU能达成了较高42倍的性能提升。(其实我个人一直都非常好奇,为什么这类应用的GPU加速是到现在才出现的…先前和做HPC的朋友聊过,他说偏门领域的这类工具普遍很弱,这也是英伟达针对任意领域写个库就马上占领市场的重要原因;不过计算光刻也算偏门吗?…)

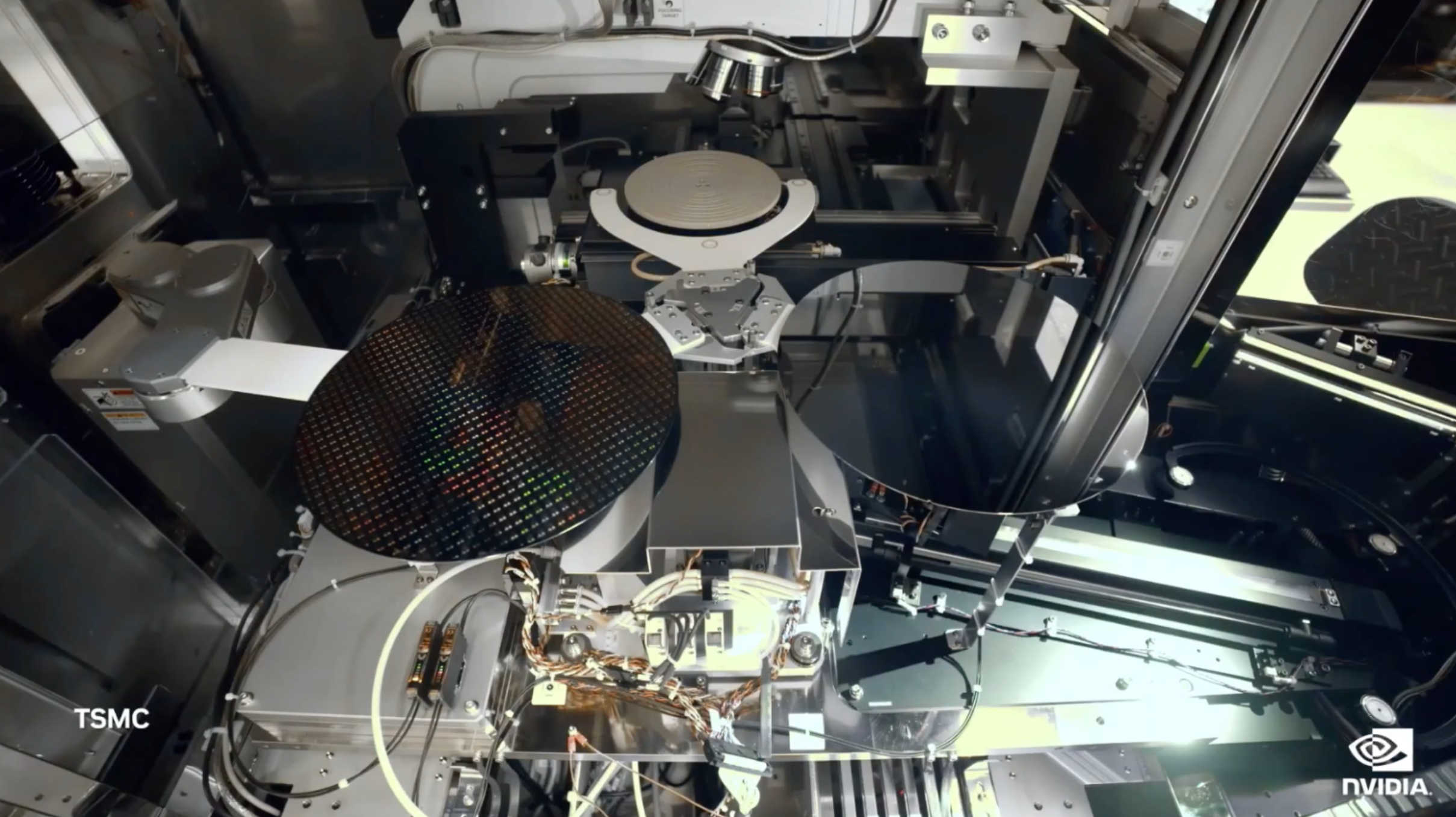

英伟达将cuLitho的价值概括成了两个方面。其一是芯片制造的生产力和效率提升——这里说的主要应该就是掩膜板制造的加速。新闻稿中说,每天生产3-5倍更多光掩膜,比现有配置节约9倍功耗。黄仁勋在主题演讲中说:“台积电在500个DGX H100系统上使用cuLitho加速,替代4万台CPU服务器,将功率从35兆瓦降低到5兆瓦。”前者相比后者是1/8的空间占用,和1/9的功耗。同时,“将原本需要2周的处理工作,缩减到一晚上就解决。(应该是说H100 GPU的单个掩膜板)”

不过据说生产工艺任何很小幅度的改动,就需要新的OPC工艺,也就需要新的光掩膜。于是英伟达在宣传中就提到,因为OPC成为芯片制造中的关键因素,所以cuLitho的价值也就不仅限于掩膜制造了,而是“任何使用这项技术的foundry厂的整体开发周期”。

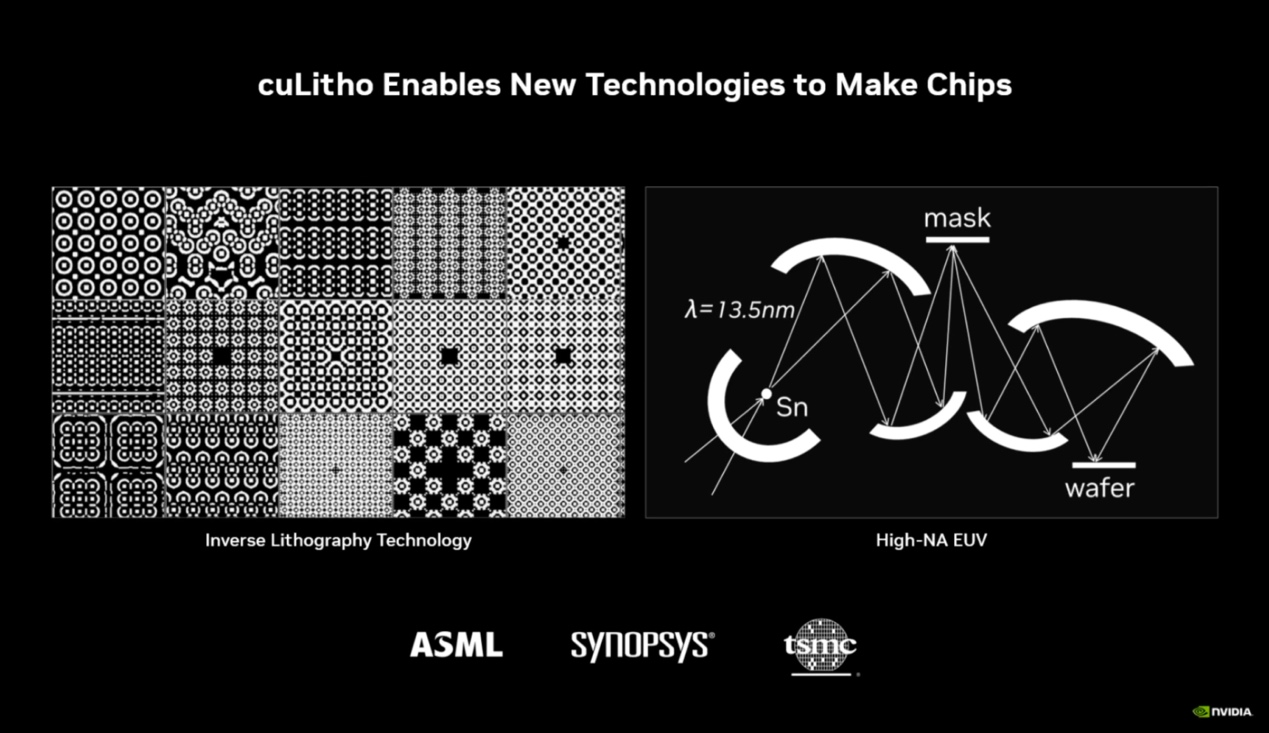

其二是,英伟达认为现在给予计算光刻的算力是不足以支撑未来的芯片设计与制造的。“这些芯片需要新的技术,可能在算力上会有10倍的需求量”。比如上面的这两个例子,曲线式ILT掩膜(Curvilinear ILT mask)和高数值孔径(High-NA)EUV光刻。后者比如说变形成像(anamorphic imaging)——这部分蔡司多年前还有过一次专门的介绍,都会是cuLitho能够加速的。

针对前者ILT,Vivek还专门举了个例子:在尖端制造工艺上,只是打几个小孔的掩膜图案就可能十分复杂了——这一点文首的例子就已经可以表现了。据说ILT还提供景深(depth of focus,可能在光刻领域这个词当译作“焦深”-但和摄影领域的景深是类似的意思)信息,就是确保光刻是在焦内的,这样晶体管和互联线路才能尽可能得清晰。如此才有更高的制造良率。“理想解决方案其实已经存在了15年了,但我们一直没有算力去广泛实施。cuLitho就提供了这样的能力。”Vivek说,“未来可能不止是用ILT会更好,而是必须使用ILT的问题。”

所以英伟达的意思就是,cuLitho不仅是用于提升效率和芯片制造良率,而且是为未来的芯片制造做准备。

如此,就算是把cuLitho解释清楚了。不过这里面还有一些关键问题,我们来尝试解读一下。

首先是cuLitho谁在用?或者说生态发展情况如何…

黄仁勋在主题演讲中特别提到了台积电、ASML、Synopsys这几个企业参与到合作中来。应该分别就代表了foundry厂、设备制造商、EDA供应商的态度。

新闻稿中提到,台积电已经在整合cuLitho软件库,Synopsys也正将其整合到EDA软件中;而ASML则是“与英伟达在GPU和cuLitho方面紧密合作,计划将GPU支持整合到所有的计算光刻软件产品中”。ASML CEO Peter Wennink也的确提到了cuLitho对于高数值孔径EUV光刻产生的价值。这三家企业CEO的评价,应该说就cuLitho的价值体现,还是相当有分量的。

第二个关键问题是cuLitho有没有AI成分。

其实这次英伟达在对cuLitho的介绍里,对于算法部分几乎是没有提及的。Vivek说,算法主要是相关于“底层的基础操作(underlying primitive operations)”。有否加入AI,我反复听了Vivek在答记者问阶段就这个问题的回答——始终也没有理解他的意思是用了还是没用。想必如果用了AI,那么英伟达应该会在这方面做宣传。所以猜测大概率是现阶段还没有用。

另外,就这个问题值得一提的是因为是“primitive operation”支持,所以据说也存在改进后用于e-beam litho电子束微影的可行性(包括掩膜本身的制造?)。

有关是否支持旧工艺的问题,Vivek也确认了是可以的。因为cuLitho就是用作提升解析力、消除衍射的计算光刻,那么对于存在这种需求的工艺来说都适用。不过我们认为,这大约还涉及到成本和foundry厂的选择问题;其中包括cuLitho究竟能多大程度提升良率。

问答环节有个比较有趣的问题是,有人问到在多重曝光的问题上,cuLitho能不能减少掩膜板的数量。Vivek的回答是“potentially”,因为像ILT的存在本身就能够减少掩膜的切分;所以“在某些情况下(in some cases)”,cuLitho达成的解决方案能够减少掩膜数量。

还有一个比较多人关心的问题是,cuLitho的盈利模式究竟是什么样的,究竟授权给哪个层面的客户,从谁那里收钱。

这个问题的答案是不清楚,英伟达尚未就其商业模式做出说明。不过可以肯定的是,cuLitho起码需要英伟达GPU支持——但不一定需要最新的Hopper架构GPU,以前的老GPU也可以,起码Volta、Ampere都可以。

另外英伟达应当也希望扩大cuLitho的影响力,不仅限于当前的三个大客户,未来就看市场的其他玩家会不会入局了。

我们仍然感觉,这其中很妙的一件事情是:台积电给英伟达制造GPU,但与此同时台积电的供应商和台积电自己又在用英伟达GPU做芯片设计与制造的加速。就好像一边说台积电用cuLitho之后节约了大量时间;另一边又说搞定H100 GPU的掩膜板节约了很多时间。这是CS与EE之间的微妙关系。

既然EDA也是这一局的重要参与者,不要忘记3月29日-30日,将在上海举办的2023国际集成电路展览会暨研讨会——本次盛会同期举办的EDA/IP与IC设计论坛上,会有Cadence、安谋科技、思尔芯等企业所做的精彩主题演讲,千万不要错过。2023中国IC领袖峰会、中国IC设计成就奖颁奖典礼等活动都会在此期间进行。关注半导体行业技术与市场最新动态,点击这里现在就报名参与。

文章来自:https://www.eet-china.com/