现代车辆中最新的信息娱乐是要求很高的功能,只有通过新的高速图形卡和超快内存存储的有效集成方可实现。人们所有的数字社交信息都被记录在机架式的大型计算机中,这就需要从执行内存驱动器中快速检索数据,然后在子系统中做循环处理。

大量的图像不断地以高分辨率拍摄和保存,并且在一些场景中被传递到AI(人工智能)服务器;在那里,复杂算法对数据进行压缩及快速处理,从而产生了出色的结果。

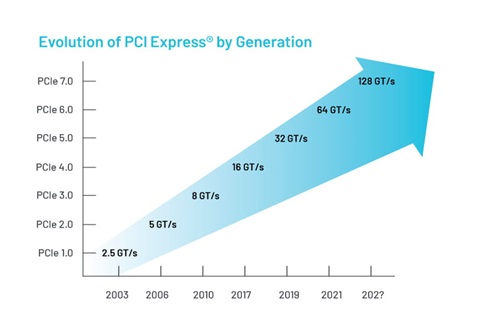

实际上,典型的AI服务器与任何其他复杂的计算系统并没有太大区别;都有一个主板和其他一些复杂的设备相互连接,如图形卡、硬盘驱动器和大量交换机。所有这些设备的标准连接都基于PCI express(PCIe)标准。自2003年发布名列前茅代PCIe®标准(图1)以来,PCI-SIG®标准一直在年复一年地执行和升级,目标是使每一代PCIe®的数据速率翻倍。

但更快数据速率的处理使得电子系统设计成为一项渐进式的改进工作,需要大量的技能和耐心。需要小心地将主板和附加卡的复杂互连系统分解成更小的子电路,这些子电路也将成为后续阶段进一步改进的目标,即使在整个设计完成之后。

图1:随着PCI Express的代际演进,数据传输速率不断提高。

随着对额外带宽的需求增加,PCIe Gen4现在已在各种市场环境中取代了上一代。为了解决这一问题,工程师们通过实践不断更新他们的设计,相互交流PCB通道布线的建议和指南,最大限度地减少串扰或解决因错误放置的通孔引起的EMI问题。

这些工程师通常是“探路者”,他们的不懈努力是确定信号的潜在损害可能发生的地方,以及信号可以容忍多少损害。包括为了降低成本更换了一个简单的连接器、由于最后的机械要求或采购问题所引起的引脚轻微变化、固件或硬件升级、或生产过程中的任何修改,都有可能成为最糟糕的噩梦,因为处理这些问题可能会导致额外成本甚至是必须重新设计。

在主板上应用BIOS更新,可能会解锁与NVMx SSD的全速通信,不过这可能会改变电气物理层的状态。在固件升级期间,连接到主板并与CPU通信的交换机和定时器的配置设置可能会发生变化;修改这些条件后运行“车道裕度测试”可能会产生不同的测试结果。抖动限制的增强可以随时发生,复杂仿真工具中的精确建模是在证明对物理层的真实影响之前执行“虚拟”验证的关键。然而,仿真并不总能够代表现实世界的真实实现,因此仍须进行物理层测试。

低功率Gen3和Gen4配置经常被重新设置,以实现潜在的节能配置。还需要对电源电路进行微调,使上电过程足够快,以满足链路对持续时间的要求,有时候即便是几毫秒的增加,可能都变得很重要,都会生成需要重新验证的新场景。

但在这些场景中,重新验证设计可能不具成本效益:事实上,对物联网/消费者应用中仍然使用PCIe Gen3连接的非关键低成本产品进行的微小设计更改,如果再花费很多时间进行实验室验证测试,就不见得存在足够的合理性。

Silicon Design公司拥有可遵循的复杂决策树,可帮助在设计变更中进行新的验证和确认测试时能够做出颇具智能的决策。这些决策树基于风险和成本评估分析。

本文中使用的测试工具通常是误码率测试仪(BERT)和示波器;这些仪器将继续提升,以满足新一代PCIe标准的性能要求,不过使用起来可能相当复杂,具体还要取决于用户的经验。

与验证和确认成本相关的不仅仅是仪器硬件成本,还包括参与活动的全职专家资源成本。为了确保与被测设备电气连接的正确性,虽然软件向导可以为每次的测试设置提供指导,但使用BERT和带探针示波器的整个过程中,仍然需要专家来监督整个过程。

让我们考虑一个所谓“链路初始化”的例子。这是一个物理层控制过程,对设备的物理层初始化并将某些设置应用于链路至关重要。在正常操作期间,此过程会自动发生,但如果要深入理解设计验证,就需要对特定数据进行编码的软件,以便用户能够诊断和监控状态转换期间信号上出现的潜在问题。BERT通常用于精确控制的链路训练和均衡,涵盖三个主要测试领域,即:合规性、裕度测试和故障检测。另外,还需要实时示波器,并且需要复杂的应用软件,以便在与BERT通信以交换设置参数数据的同时,在接收终端侧自动执行复杂的测试程序。

裕度测试还要求在PCIE槽的每个通道上按顺序重复一系列固定步骤,包括触发电压时间设置调整。这种涉及不同复杂仪器的漫长而复杂的程序可能会引入人为错误,从而降低整个验证过程的效率。

Tektronix不是寻找BERT/Scope系统的替代品,或者是已经现成的且广泛使用的片上通道裕度(LM)工具,而是采取了不同的解决方案。

图2:TMT4裕度测试仪。

图2所示的TMT4裕度测试仪基于Intel Stratix 10 FPGA,为PCIe第3代和第4代设备的链路健康评估提供了业界所需的各种功能。

TMT4裕度测试仪可连接到大多数常见的PCIe链路,如CEM、M.2、U.2和U.3,能够与当今可用的大多数PCIe设备连接。

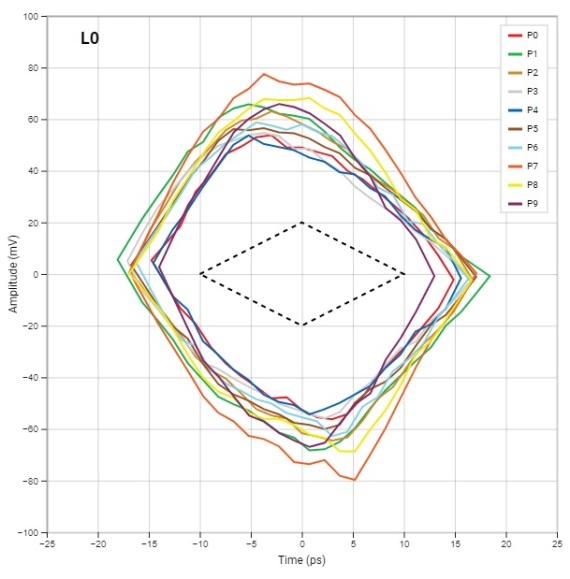

除了显示眼图(图3)之外,裕度测试仪还提供了所生成眼睛高度和宽度最大化时各接收器的均衡状态。

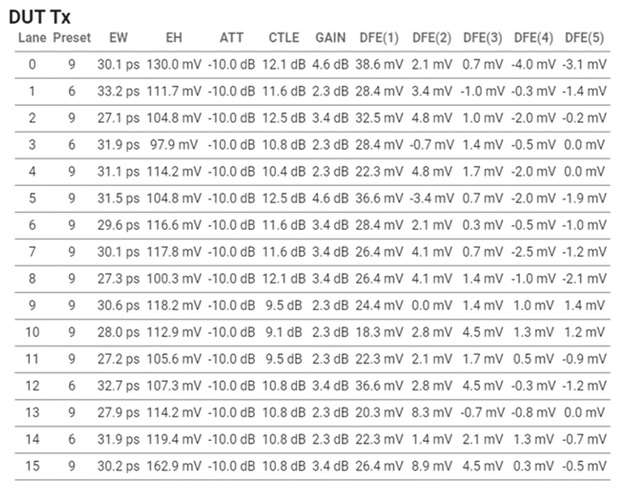

系统为发射机测试提供了两个关键数据:每条通道的眼图,以及在裕度测试仪接收端测量的预置组合(图4)。裕度测试仪的相关接收机训练值被用来打开所显示眼图的眼睛。

在接收端,可以执行被测设备的接收机通道的功能评估;在预期的操作范围内并在返回错误之前,有可能实际确定从裕度测试仪发送的信号幅度可以减小多少。

图3:TMT4裕度测试仪向用户实时呈现眼图。

图4:裕度测试接收机的链路训练参数为潜在的链路健康问题提供了额外洞察。

新的TMT4裕度测试仪提供了额外的专门用于传输/接收通道裕度测试的附加工具,使用户在短短几分钟内即可捕获PCIe Gen 3和Gen 4设备信号通道的链路健康问题。

(参考原文:Improving simplicity and efficiency on Margin Test)

本文为《电子工程专辑》2023年3月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅

文章来自:https://www.eet-china.com/