软件控制的硬件正在改变业界技术格局,而无线电硬件也被毫不例外地卷进了这一快速发展进程中。软件无线电(SDR)通过对无线电硬件抽象化来实现基于软件的接口,已获得了巨大吸引力。SDR用例已广泛涵盖了通信系统、国防、航空航天、测试测量、信号情报(SIGINT)和频谱监测等众多领域。

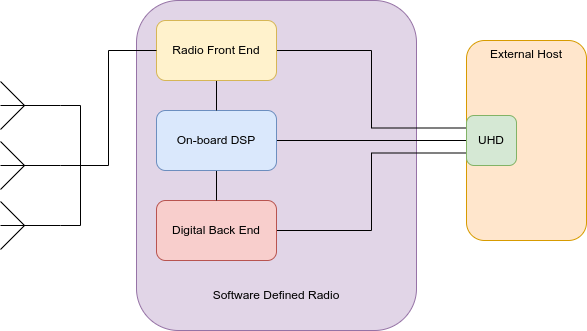

传统意义上的无线电硬件是高度专业的,包括高密度集成的微波硬件和各种特殊应用的集成电路。而SDR则抛弃了这种模式,而是利用现场可编程门阵列(FPGA)和高度可重配置的硬件来创建通用的无线电平台。在如图1所示的实现方案中,SDR将无线电前端(RFE)和数字后端(DBE)分离开来。硬件和软件的解耦,使得先进的数字信号处理(DSP)能以一种与平台无关的方式与无线电硬件紧密结合起来。

图1:软件无线电基本架构。

大多数SDR中的RFE包含多个独立且高度可重配置的发射(Tx)和接收(Rx)链路。简单的SDR载频在数GHz范围内,带宽为几十MHz,而非常先进的SDR通常涵盖从接近直流到18GHz的载频范围(一些SDR甚至高达40GHz),每个收发链路的带宽可高达3GHz。SDR的Tx和Rx链路有许多配置可供选择。入门级SDR通常是两个收发链路共享本地振荡器,而高性能SDR则可以有多达16个独立的收发链路。

与传统的无线电系统不同,SDR集成了FPGA,可以实现高性能的可重配置DSP。像调制、解调、分组和预处理等DSP功能,可移至板载FPGA来提高效率。这是SDR相对于基于ASIC的传统DSP架构的一个明显优势,因为这种架构可以很方便地植入新功能。

尽管FPGA可以提高DSP处理速度,但在主机系统和SDR之间,仍然有数据需要传输。在较简单的SDR中,USB可用于此目的,但更宽带宽SDR需要基于光纤的数据回传,才能适应RFE带宽。借助VITA49等标准化协议,数据可以很方便地传送给主机系统,以便实施进一步处理和存储。

由于通用型硬件驱动器(UHD)的普及,有很多种计算平台可用来实现基于主机的DSP。UHD是一种开源的驱动器,已经成为SDR的一种事实性标准。UHD能够与GNU Radio、GNU Octave和Simulink等工具无缝集成在一起。还可以将Python和C++与UHD结合在一起,轻松实现定制的SDR应用。UHD的开源性是非常有益的,因为它与供应商无关,所以能够提供SDR平台之间的可移植性,并有丰富的生态系统可供利用。

宽带宽的SDR提供了很大的平台灵活性,但宽带宽需要在SDR和主机系统之间建立高速数据回传。对于预处理和过滤任务,可以很方便地在采用FPGA架构的SDR上执行。但将数据转移到外部系统实施进一步处理和存储时,通常就需要一个精心设计的主机系统。无线电链路中的信号接收路径通常始于天线输入端,而终止于将数字化数据传递给FPGA的模数转换器(ADC)。FPGA接着将数据发送给外部主机上的网络接口卡(NIC),发送路径基本上与接收链路相反,只不过转换器用的是数模转换器(DAC),而不再是ADC。

主机系统和信号路径必须要仔细设计,确保各级都有充足的缓冲和处理能力。否则,将会发生接收链路缓冲区上溢和发送链路缓冲区下溢现象,进而造成数据丢失。缓冲问题不仅会造成数据丢失,而且还会导致严重的抖动,进一步损害数据完整性。因此必须精心设计收发信号链路,确保SDR的吞吐量要求能够得到满足。

SDR的一个主要好处是其所提供的灵活性,因为可以迅速被集成到各种应用中,包括频谱监测、雷达和无线通信。频谱监测和SIGINT应用通常都有宽带操作要求。拥有可重配置的多通道ADC和完全独立接收链路的SDR,支持单个SDR在对宽带宽进行监测的同时,以更好的噪声特性对窄带宽进行捕获。

尽管独立的收发链路将SDR定位为频谱监测的优异选项,但也是支持高性能雷达应用的绝佳选择。相控阵列雷达系统需要精确的时钟分发,以实现相位稳定和相干性。多通道SDR的高密度集成时钟,可以支持新的雷达无线电硬件设计或现有硬件的升级。因此,高性能SDR可以减轻设计负担,并降低给定系统的总成本。

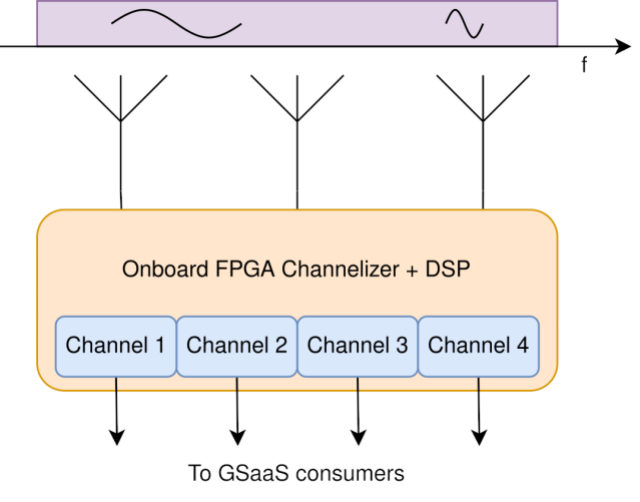

近年来,低地球轨道(LEO)卫星在通信系统和科学进步方面获得了长足的发展。这种发展为地面站即服务(GSaaS)开辟了一个市场,因为它将消除或减少卫星对专用地面站的需求。为了实现可行的商业扩展,用于GSaaS的SDR需要在范围非常大的带宽内捕获数据,从而导致数据量爆增。这对大多数下游系统来说是有问题的,不过基于FPGA的信道器(图2)完全可以胜任这类数据提取和处理。

图2:基于FPGA的具有多个独立通道的信道器。

SDR正在迅速改变无线电技术的发展历程,许多民用和国防应用可以从SDR所特有的快速创建和更新硬件平台特性中获益。面对宽带宽无线电的需求,高性能SDR是一种很自然的解决方案,因为它们具有宽带宽无线电链路、板载FPGA和基于光纤的数据回传功能。

通过将软件的敏捷性植入硬件中,可以实现更快的迭代速度,从而更好更快地开发出新一代解决方案。

(参考原文:Software-Defined Radio Brings Agility to Hardware Design)

本文为《电子工程专辑》2023年4月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅

文章来自:https://www.eet-china.com/