之前没多久,包含一百万只晶体管的系统级芯片(SoC)还曾被认为是大型器件。可如今,包含多达10亿只晶体管的SoC已是常见,例如,SiMa.AI的最新案例研究及其新的机器学习(ML)芯片MLSoC。该芯片能在嵌入式边缘提供轻松的机器学习。

MLSoC是在16纳米技术节点上创建的,由数十亿只晶体管构成。正如当今SoC设计中几乎无一例外的情况一样,MLSoC构成中,也采用了多个现成的第三方知识产权(IP)块的复杂组合,外加自己开发的机器学习加速器(MLA)IP。

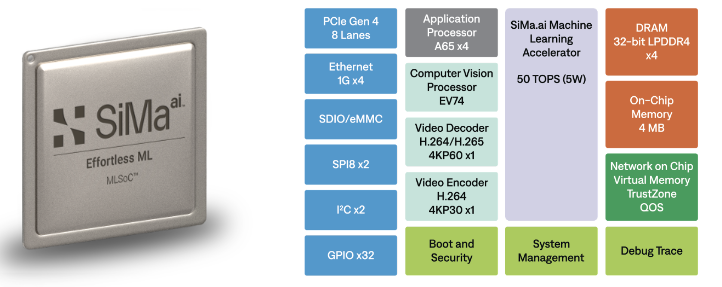

图1:MLSoC在单芯片中同时实现了主机处理器和ML加速器功能。来源:SiMa.ai

第三方IP是众所周知的标准功能,例如处理器和通信核心以太网、USB、I2C、SPI和外围器件,这些功能不值得自己花费时间和精力来亲自开发。与其竞争对手相比,MLA是这款SoC的“杀手锏”,可提供每秒50万亿次操作(TOPS),而功耗则低至5瓦。

不过,结合来自不同供应商的数百个IP所带来的一个问题是,SoC行业已经定义并采用了多个互连协议,包括OCP、APB、AHB、AXI、STBus以及DTL,其中的每个IP都可能使用不同的协议。此外,每个IP可以支持不同的数据宽度并采用单独的时钟频率。正如可以想象到的那样,让这些IP彼此交互可能会让人望而生畏。

连接数百个不同IP的优异解决方案是使用片上网络(NoC)。利用缓冲和交换,NoC在发起IP和目标IP块之间传递数据包。每个数据包都包含一个标头,其中包括一个带有源地址和目标地址的ID,以及一个包含数据的主体。大量的数据包可能会同时并发传递。

每个IP都有一个或多个称为”插座”的接口。网络接口单元(NIU)将IP”插座”连接到NoC,并对数据进行串行化和打包,同时满足每个IP的数据宽度和时钟频率要求。

开发人员通常将IP设想成在硅芯片的表面上有正方形或长方形的占位面积。尽管NoC跨越了整个芯片,但许多开发者并没有意识到它还是一个IP。

SoC开发人员必须决定是在自己实施NoC更好,还是从第三方供应商那里获得。对于许多团队来说,也许这根本就是不值得考虑的问题,因为他们完全缺乏从头开始开发全功能NoC所需的时间、资源和技能。

创建适用于现代SoC的NoC至少需要六名工程师满负荷工作两年。然后还有同时调试NoC和其他一些设计问题。少数能够降低风险、加快上市时间(等同于货币化时间)的现实解决方案,就是选用可信供应商经过验证的现成NoC。

不仅仅需要将NIU连接到IP”插座”,还需要确定任一交换机的位置以及任一缓冲区的大小和位置。由于NoC横跨整个芯片,因此有必要为物理布局团队和工具引入多级管道(寄存器),以满足SoC的性能和时序规范。

设计还包括迭代。在流程的前端设计部分执行迭代,要比包括前端和后端物理布局要快得多。如果前端设计工程师手动插入各级管道,并且未能在正确的位置使用足够的资源,则后端物理实现团队将无法实现其目标,导致项目会被退回返工。

不幸的是,架构师通常会通过过度开发、并插入过多级的管道来解决这个问题。尽管这将有助于物理设计团队满足时间要求,但任何超出需求的管道级数都会消耗管芯面积、加大功耗并增加延迟。

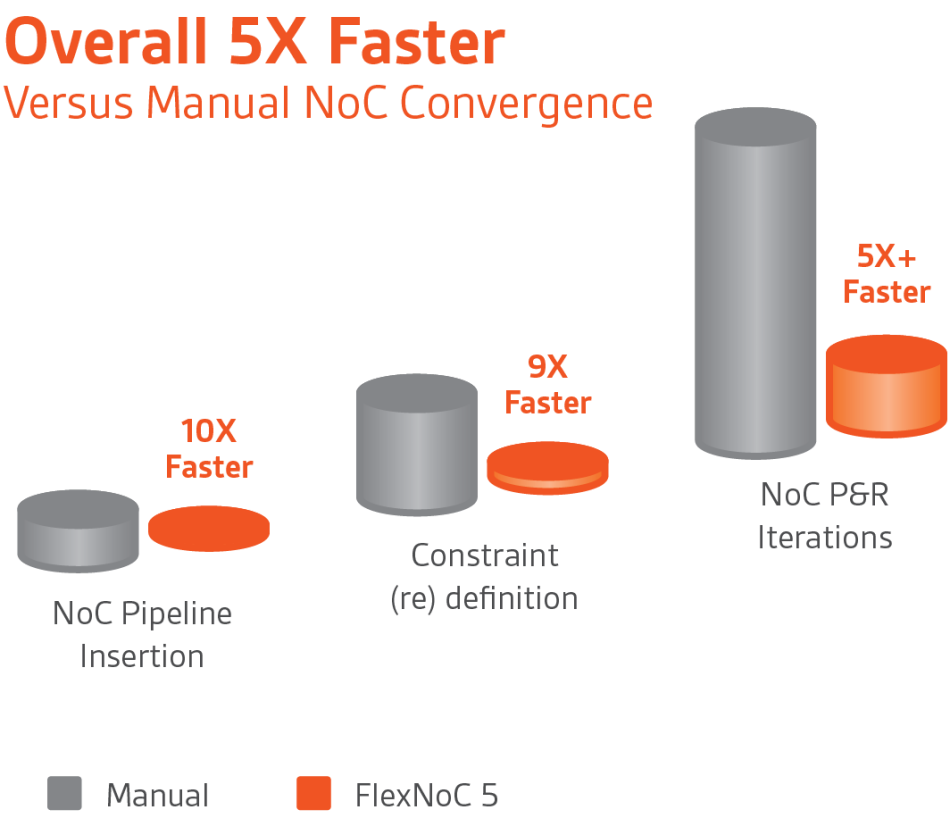

解决这一问题的一种正确方法是使用物理感知NoC。这意味着,一旦物理布局团队提供了各个IP块的建议位置,该数据就可以用于自动确定优异的管道级数和位置。通过加快物理布局过程,实现时序收敛所需耗时的后端到前端迭代次数显著减少。

FlexNoc 5就是一款这样的NoC,它具有物理感知能力,还有一些其他功能选项。对于具有数百个IP和1024+位宽连接的拔尖设计,FlexNoc XL选项提供了大容量网状NoC生成器功能。FlexNoC 5高级内存选项适用于复杂内存交织方案和非连续地址位的架构。此选项使用多通道缓冲区重新排序,以避免排序规则块和响应序列化瓶颈,同时支持并发内存通道读取。

图2:物理感知片上网络IP可提高生产力。资料来源:Arteris

有些设计是安全关键型,这意味着故障或误操作有可能会导致人员严重受伤害甚至死亡,或者是设备和财产损失甚至严重损坏,或者是危害环境。在这种类型的设计中,FlexNoc 5 IP可以通过FlexNoc快速还原能力选项来补充。该软件包可帮助设计人员实现符合汽车ISO 26262和IEC 61508标准所需的安全功能。它还为增强型企业SSD耐久性提供了所需的硬件可靠性。

管理复杂SoC设计的少数方法是使用NoC。与其花费数年时间并消耗大量工程资源来自己开发,不如选用可靠的现成NoC,以节省开发时间、降低风险并加快上市时间。

(参考原文:Create high-performance SoCs using network-on-chip IP)

本文为《电子工程专辑》2023年5月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅

文章来自:https://www.eet-china.com/