电子工程专辑讯 台积电、三星、英特尔等晶圆制造大厂都在积极布局背面供电网络技术(BSPDN),并将导入尖端的逻辑制程的开发蓝图。近期,三星电子公布了 BSPDN(背面供电网络)研究成果。这是三星电子首次披露BSPDN相关的具体研究成果。

BSPDN是2019年IMEC上首次提出的概念。它是一种通过在晶圆背面布置电源布线来改善电源和信号线以及电池利用率瓶颈的设计结构。

当前的半导体采用 FSPDN 结构制成。它们按照电源线-信号线-晶体管的顺序排列,但由于电源线和信号线使用相同的资源,会出现瓶颈等问题。另外,还存在一个缺点,即根据晶体管的扩展而消耗大量成本来扩展布线层。

与现有的半导体结构不同,BSPDN按照信号线-晶体管-电源线的顺序排列。在今年6月底的日本 VLSI 研讨会上,三星电子发表的一篇论文称,通过应用 BSPDN,与 FSPDN(前端供电网络)相比,成功缩小了 处理器面积的14.8% 。具体而言,在两个ARM电路中,面积分别减少了10.6%和19%。这也意味着成本和功耗的降低。同时也意味着,如果芯片面积保持不变的情况下,芯片内部的晶体管数量可以增加10% 到19%,性能也有望提升10%到19%。除此之外,其背面供电技术还能使得布线长度减少了9.2%

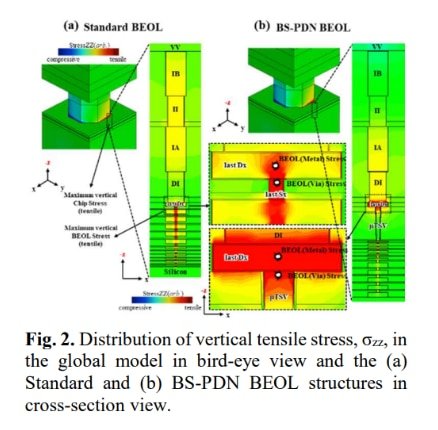

三星电子也解释了BSPDN的技术难点。当应用BSPDN时,拉伸应力作用,并且可以将硅通孔电极(TSV)和金属层分离。三星电子表示,这个问题可以通过降低高度或加宽TSV来解决。

除了三星电子之外,英特尔也公布了其命名为“PowerVia”的背面供电技术,将导入Intel 20A制程工艺。英特尔去年六月还举办了Powervia技术简报会。这些公司的目标是从 2nm 工艺开始应用 BSPDN。

根据英特尔的Blue Sky Creek的测试芯片(该芯片采用英特尔即将推出的PC处理器Meteor Lake中的P-Core性能核心),证明了PowerVia解决了旧的“披萨式”制造方法所造成的问题,即电源线和互连线可以分离开来,并做得线径更大,以同时改善供电和信号传输。测试结果显示,芯片大部分区域的标准单元利用率都超过90%,同时单元密度也大幅增加,并有望降低成本。测试还显示,PowerVia将平台电压(platform voltage)降低了30%,并实现了6%的频率增益(frequency benefit)。PowerVia测试芯片也展示了良好的散热特性,符合逻辑微缩预期将实现的更高功率密度。

业界认为,为了应用BSPDN,确保晶圆背面处理的化学机械抛光(CMP)技术以及信号线和电源线连接的TSV技术非常重要。台积电将会在 2025 年量产2nm(N2)工艺,并计划 2026 年推出 N2P 工艺,这个工艺也将会采用背面供电技术。

三星尚未透露计划何时实施其 BSPDN 以及使用哪个节点。该公司目前正在完善其第二代基于 3nm 级环栅晶体管的 SF3 制造技术,并计划于 2024 年实现量产。该公司还有 SF3P 和 2nm 级 SF2 将于 2025 年推出。尽管三星明年不太可能在 SF3 中使用背面电源轨,但该公司可能会考虑在 2025 年在 SF3P 或 SF2 中实施其 BS PDN。

文章来自:https://www.eet-china.com/