Intel刚刚发布的电脑处理器Meteor Lake基于Intel 4制造工艺,并采用Foveros 3D封装方案。尤其后者,或许对PC处理器而言,意味着一个新时代的开启;chiplet和先进封装真正要走进千家万户了;Intel说这是40年来最大的处理器架构变革…

有关代号Meteor Lake、用于PC的新一代酷睿Ultra处理器,大框架的技术点我们已经在前篇文章做了介绍。Meteor Lake之所以受人瞩目,品牌名还改做了“酷睿Ultra”,很大一部分原因是这代芯片,部分基于最新的Intel 4制造工艺;与此同时还用上了chiplet、先进封装这些热门技术。

其实我们过去对Intel 4制造工艺,以及EMIB、Foveros先进封装技术已经多有报道。但这次Intel Innovation上,随Meteor Lake的发布,Intel又做了一些信息的更新。本文就来谈谈Intel 4工艺,以及在Meteor Lake处理器上应用的先进封装技术。

这次的媒体会上,Intel说Intel 4的量产意义很大,是此前Intel承诺的“四年5个节点”“非常重要的里程碑”,“会对Intel 3、20A、18A工艺起到促进作用”。

Intel现在似乎不喜欢人们将其工艺和“几nm”挂钩。不过去年年中,我们就在《Intel 4工艺剖析:可以算是4nm吗?》一文就其定位做了明晰,即便Intel不愿意将Intel 4和4nm这个称谓扯上关系,Intel 4也的确在很多维度上超过了另外两家foundry厂的4nm工艺,并且明显和3nm更接近。

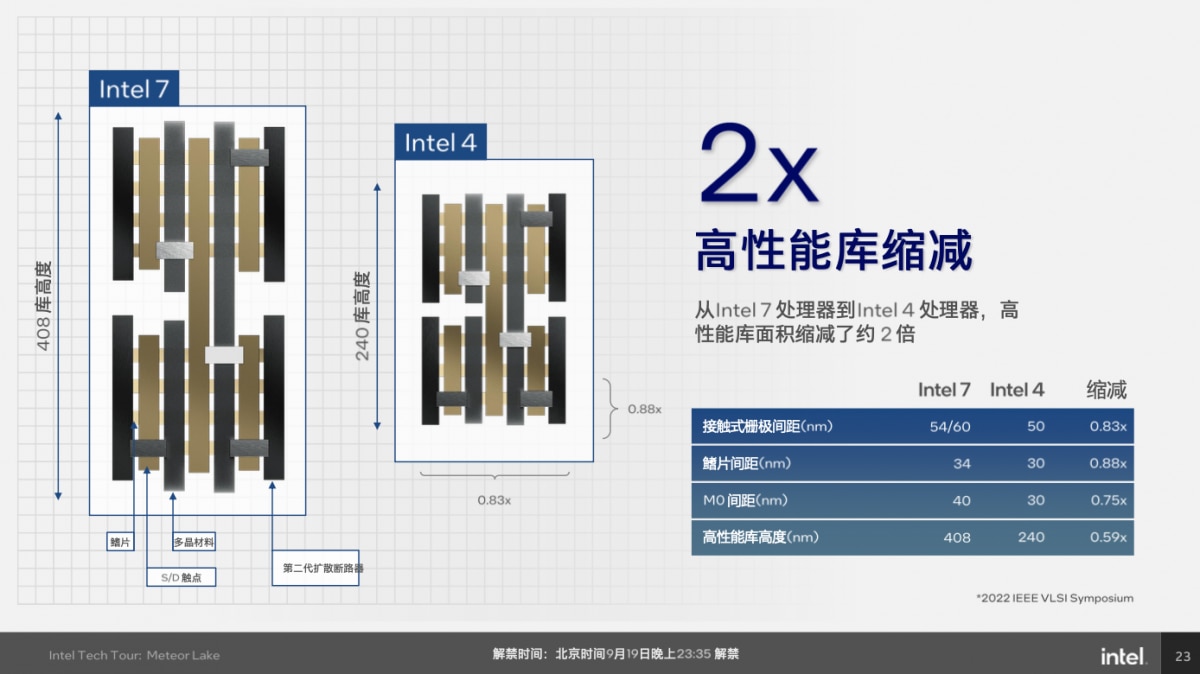

在去年的IEEE VLSI研讨会上,Intel就明确过Intel 4的HP高性能单元库面积缩减2倍,或者说晶体管密度相较Intel 7提升2倍。

上面这张图给出了Intel 7和Intel 4高性能库的尺寸,以及关键参数——包括fin pitch、金属层M0间距、contacted poly pitch等。具体的之前我们都介绍过了,就不再赘述。

不过依旧要强调一点,就是Intel 4这代工艺只做了HP高性能库,而没有做HD高密度库。所以这里的密度提升2倍,是前后两代HP库的比较。此前Intel就说过HD库会留待Intel 3节点时实施。

对于Meteor Lake而言,Intel 4的HD库缺失其实无关紧要,因为Intel 4主要用于这颗芯片的Compute tile,也就是CPU所在的那片die;其余die/tile的工艺可能都有差异,有些是由第三方foundry制造的——这也充分体现了Intel现如今的IDM 2.0战略。

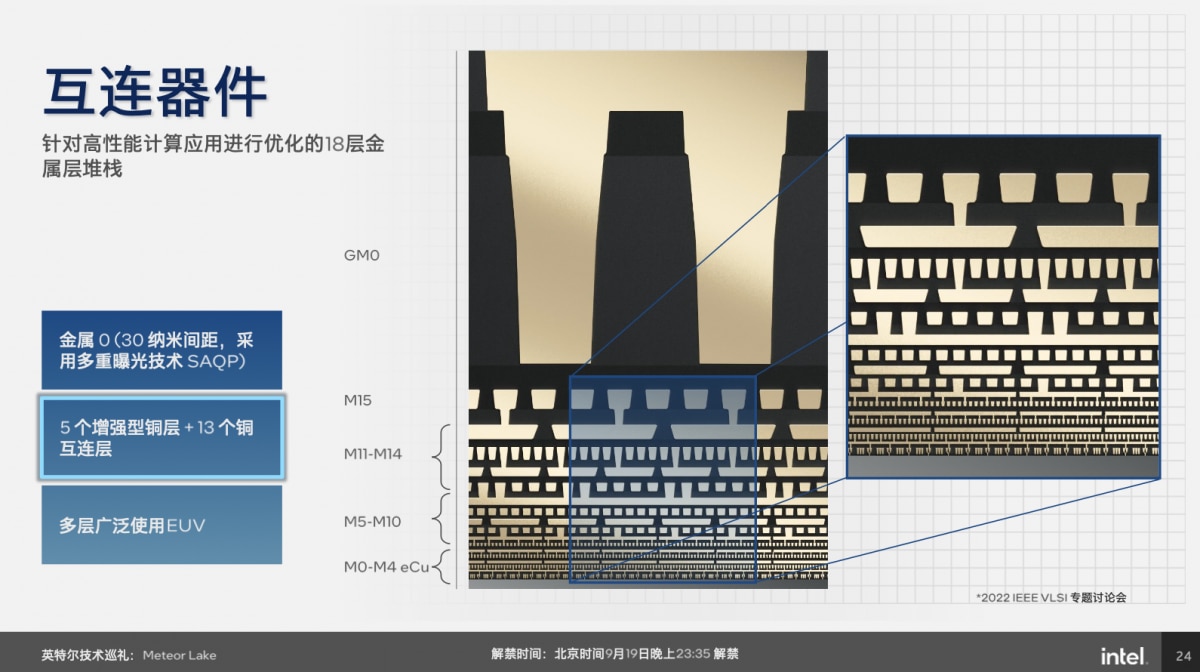

Intel 4在互联金属层部分,除了间距缩减,相比Intel 7多了1层M15;真正开始在某些层上使用EUV极紫外光刻;且底层的材料使用上也发生了很大的变化。主要是M0-M4这5层的金属线,换成了所谓的eCu(增强型铜)。

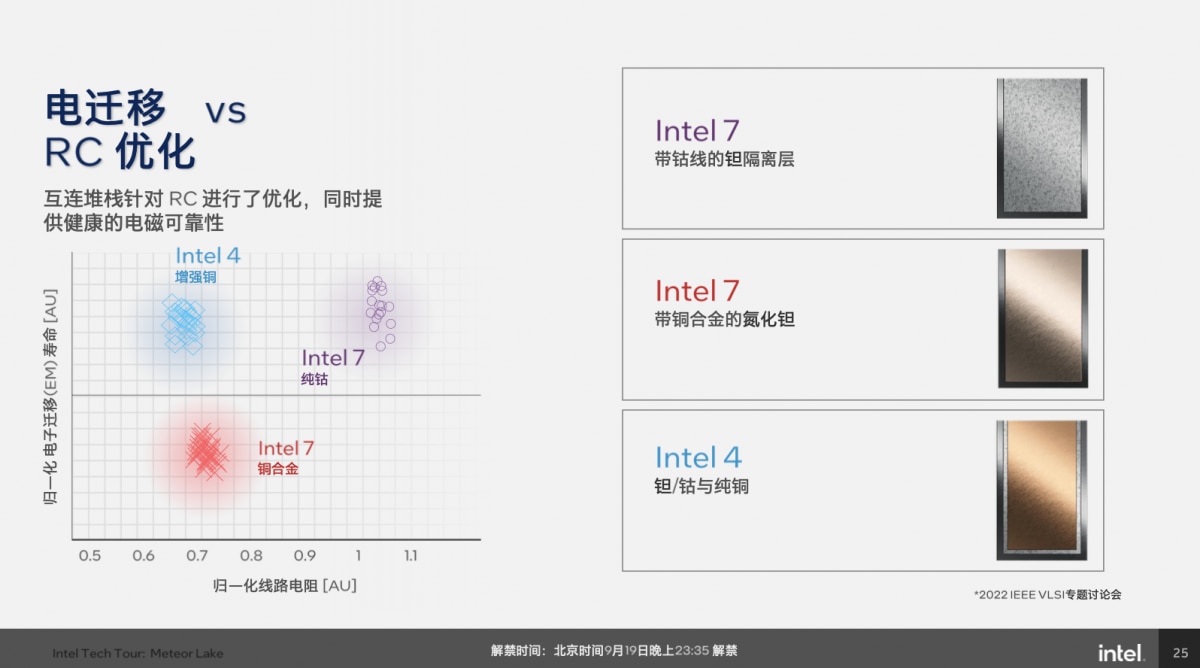

这种eCu实际上是铜外部覆盖钴,最外层diffusion barrier则为钽。关注Intel制造工艺的读者应该会比较了解,在Intel的10nm工艺时代,最初就很激进地选择了钴材料。不谈电阻率的问题,这可能也成为10nm(包括Intel 7)此前迟迟未能步入成熟期的重要原因。

实际上钴的电阻率是高于铜的,所以其导线电阻本身也将更高——这是对钴而言的显著不利因素。此前Intel之所以换用钴,是考虑到铜的电子迁移(electromigration)问题。随工艺节点持续迈进,金属层线宽(line width)也变得更小。钴的特性,决定了导线外部的barrier层可以做得很小,钴的line core width则保持住宽度,电子迁移的问题就会比较小——而铜在这方面就是个大问题。

但大概是存在实施上的技术难度,以及考虑钴毕竟还是有着显著更高的电阻率,Intel也就对这部分做了改良。Intel 4的eCu方案达成了更低的线路电阻,而且电子迁移带来的寿命问题也达到了钴相似的水平,如下图:

Intel 4工艺还有一些关键点,包括“广泛使用”EUV极紫外光刻,不仅提高了图案的保真度,而且减少了总的掩模数和工艺总步骤——这个好像是三星、台积电也都不忘宣传的。如果说相同图案的曝光,据说工艺步骤能减少3-5倍。

Intel给的数据是,芯片在采用EUV光刻的情况下,Intel 4工艺相较于Intel 7总体少了20%的掩模数,工艺步骤则减少了5%。毕竟如果不用EUV,而继续用DUV多重曝光的话,Intel 4相比Intel 7必然会大幅增加工作量。

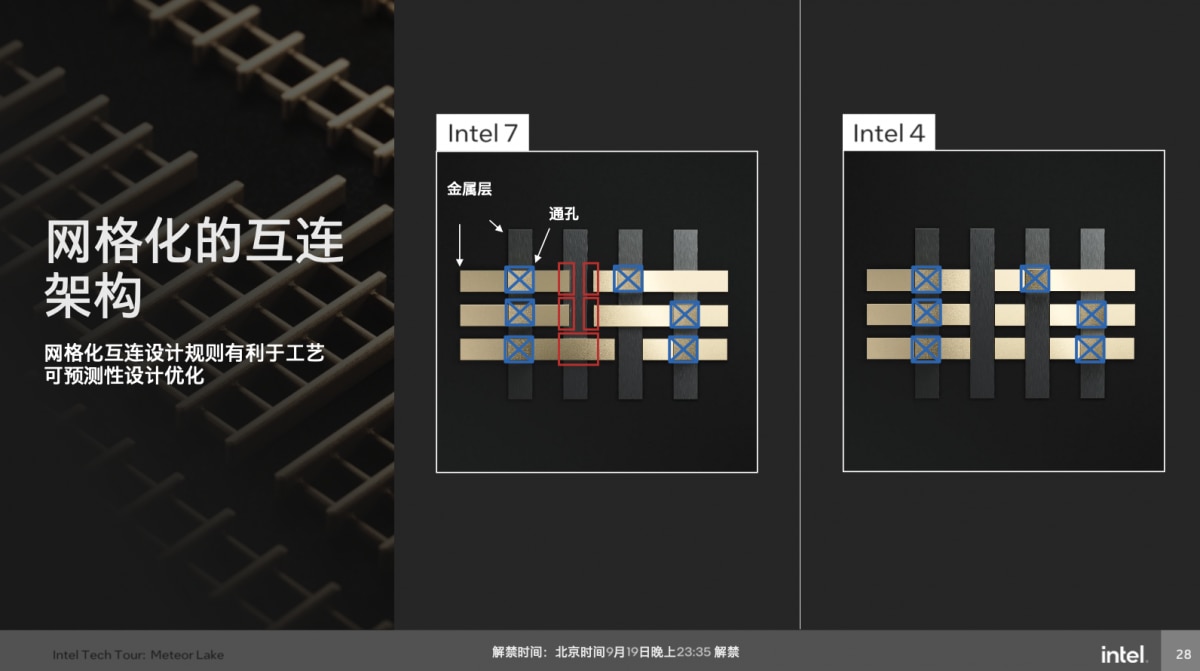

另外基于EUV还带来了一个好处,互联结构变得更加“标准化”。Intel 7由于尚未使用EUV,带来了不少非标准的连接方式;EUV则带来了更为统一的“网格化互联设计规则”。

Intel方面说,这对于APR工具(auto placement & route)变得很重要,“在没有特殊件的情况下,布局、单元摆放、时钟树统一(CTS)、布线等都更容易实现”;在Intel 7时代,“必须要要用特殊件,要做非常仔细的分布,以免出现摆不好或者放不下之类的情况”。

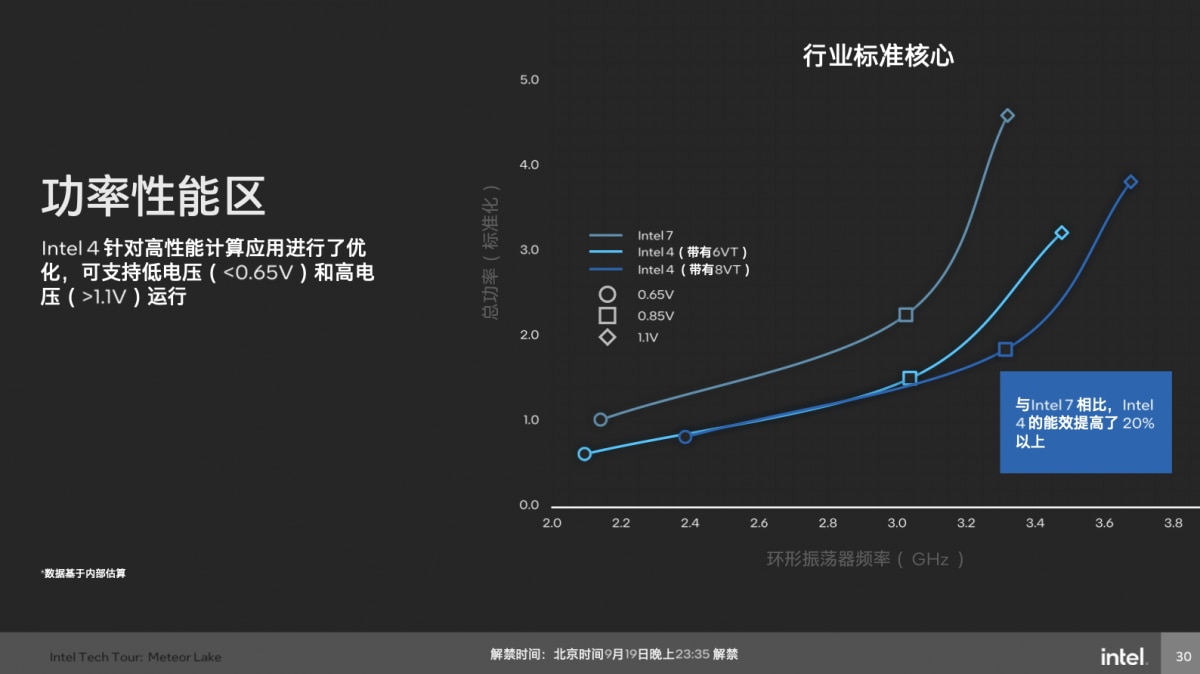

有关Intel 4达成的PPA提升,之前Intel也提过。基于行业标准核心(应该是Cortex-A76),采用Intel 4相比Intel 7在时钟频率方面最多可提升21.5%。即Intel 7工艺达到2.1GHz频率时,同功耗下Intel 4能多出21.5%的频率;而2.1GHz同频率下,Intel 4可降低40%的功耗。

Intel 4的极值频率多了5%的余量,是8VT(4N+4P,可能是一种HVT晶体管)选择带来的更高的极值性能。不过注意,从下面的图也不难发现,这不是基于x86的核心IP;Meteor Lake即酷睿Ultra产品层面应当会揭晓这方面的数据。

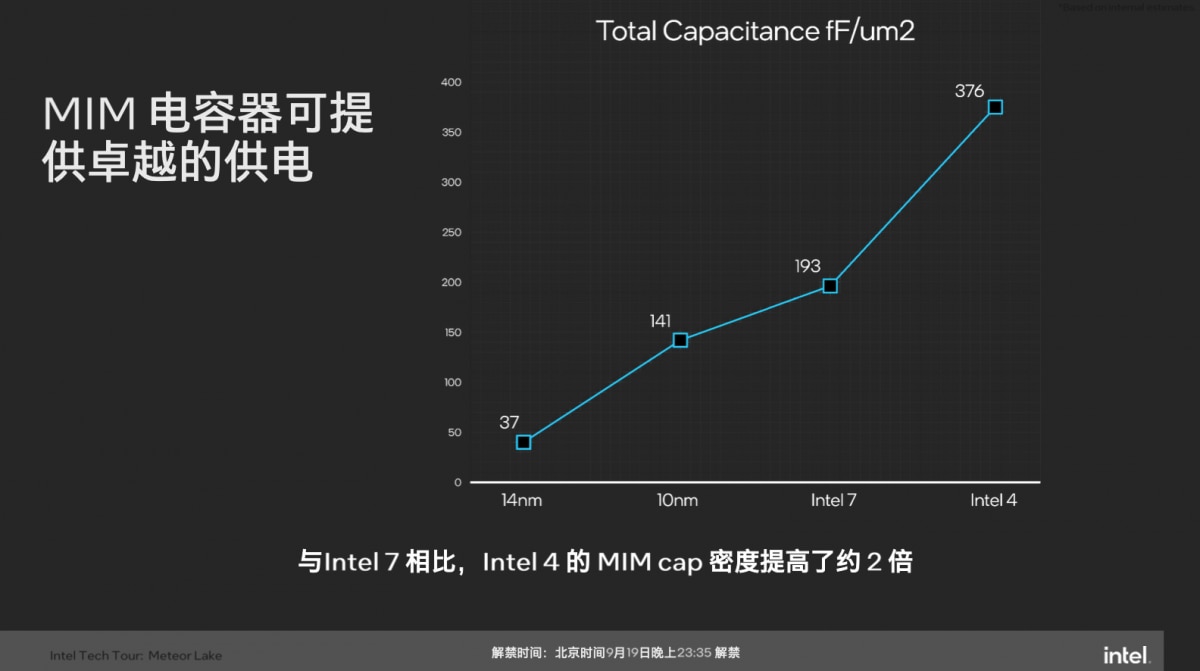

还有一项关键更新是Intel 4的MIM(metal-insulator-metal)电容密度提高了大约2倍,属于金属互联高层部分的SuperMIM电容迭代。此前Intel 7还叫10nm enhanced SuperFin时期,Intel提及过SuperMIM的更新。

当时Intel就说采用一种新型的SuperMIM,相比面积相似的业界标准MIM,电容量增加5倍,实现电压降低和性能提升。其中关键是通过新型high-k材料在<0.1nm的薄层中沉积,在两个或多种材料类型之间构成所谓的superlattice超晶格。

Intel 4这部分的提升详情,Intel没有在本次媒体会上多谈;只是提到376 fF/μm²的电容密度。具体如下图:

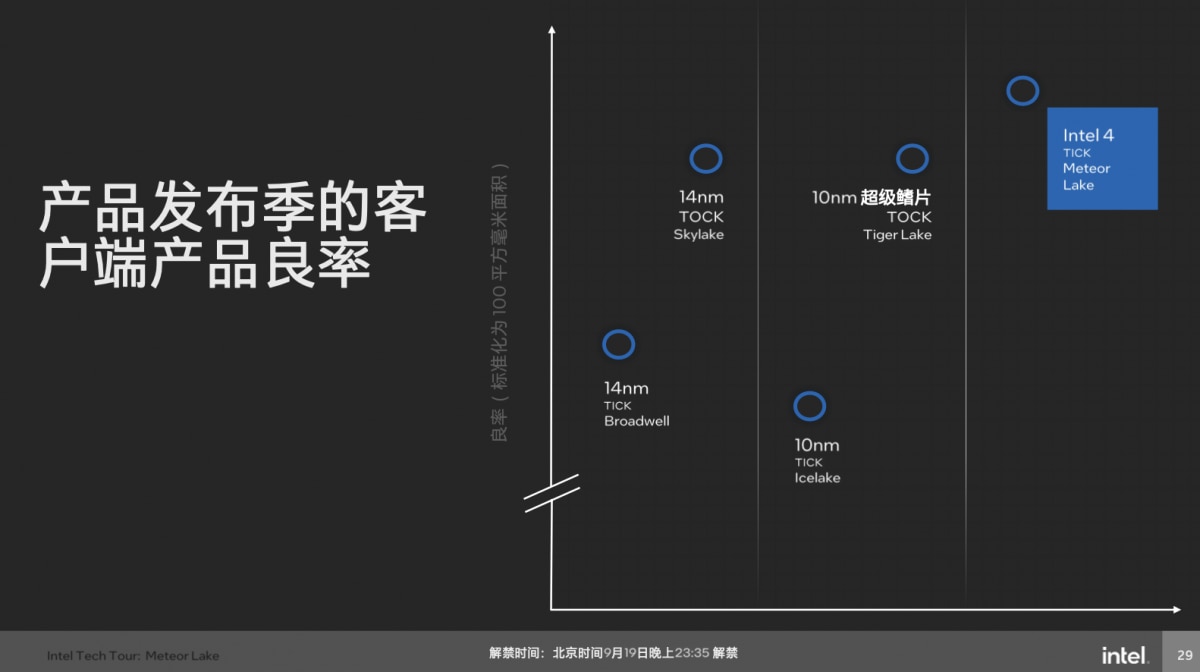

有关Intel 4最后值得一提的是良率。据说Meteor Lake的良率很高,基本超过了14nm和10nm成熟期的良率水平。下面这张图提供了良率的相对值,可见已经高于Skylake和Tiger Lake。

像Tiger Lake,理论上应该已经算是Intel 10nm的第三代了。Intel愿意在Meteor Lake发布之际呈上这样的数字,一方面是给予市场信心,另一方面应该也是为接下来Intel 3要提供foundry服务做前期宣传。

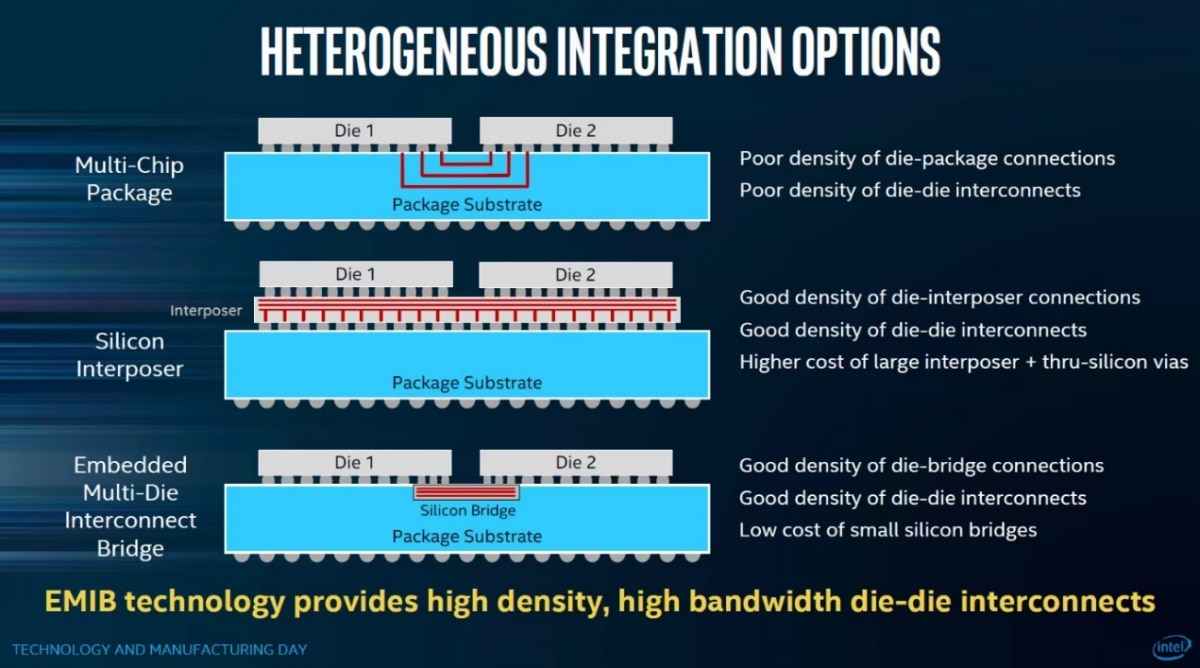

其实Intel最知名的两类封装方式,EMIB和Foveros,我们之前也写过好些文章做过介绍了。前几个月,我们和几家半导体封装设备厂聊了聊,进一步明确了“先进封装”的概念。行业普遍是把互联密度足够小的芯片倒装(flip chip)也算做先进封装的。

而一般我们大部分人理解,相对狭义的“先进封装”是特指2.5D和3D封装,也就是将不同的chiplet基于硅桥(silicon bridge)或者某种中介(interposer)“连起来”的封装方案。

Intel EMIB(Embedded Multi-Die Interconnect Bridge)就属于一种基于硅桥的2.5D封装方案,就是在chiplet之间,在封装基板上“挖出”硅桥通路,如上图中的最后一类方案;EMIB达成的IO互联间距为55μm。比较知名采用了EMIB封装的芯片如4代至强Sapphire Rapids。

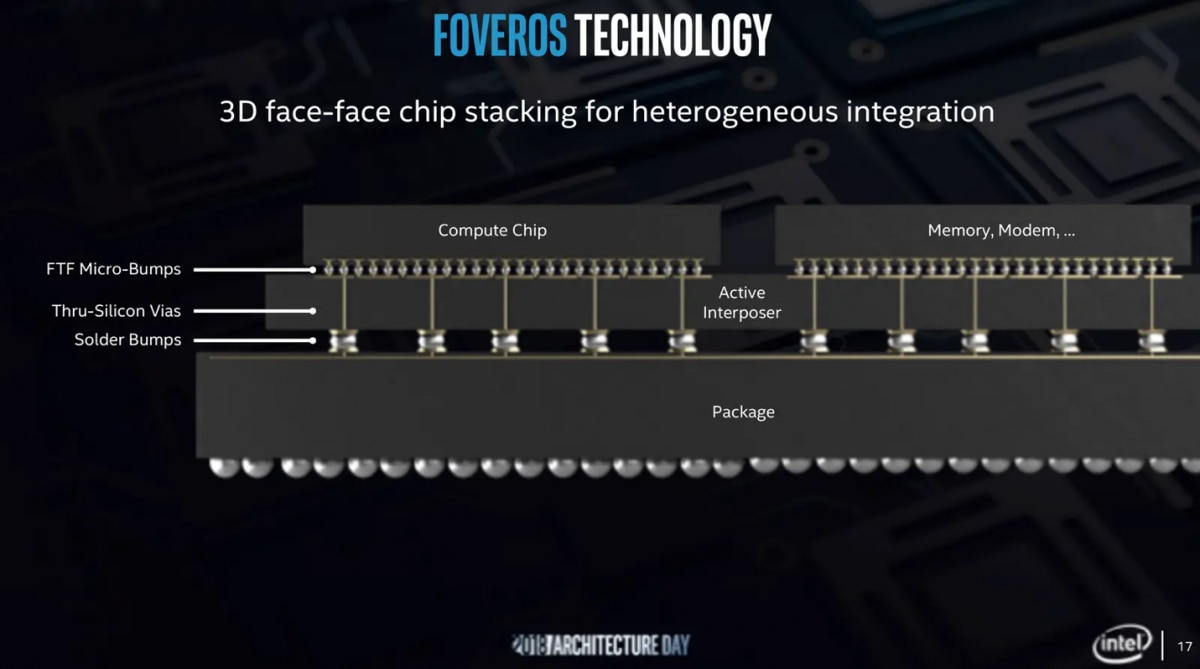

Foveros在Intel看来完全属于3D堆叠方案,就是把chiplet/die面对面叠起来——比如下图中上两层通过μbump互联堆叠方式。我们最早见过基于Foveros做3D堆叠的芯片是2020年少批量生产的Lakefield。当时Lakefield基于Foveros叠了base die和compute die两层。其中compute die主要是CPU和GPU,而base die就是cache和IO了。

虽然就interposer的角度来看,它其实多少有些像是2.5D封装。不过Foveros作为一个品牌,本身也在不断迭代,或者说有不同的技术版本。比如说Foveros Omni、Foveros Direct等。其中第四代的Foveros Direct就是传说中的hybrid bonding混合键合了,据说互联间距可达成10μm。

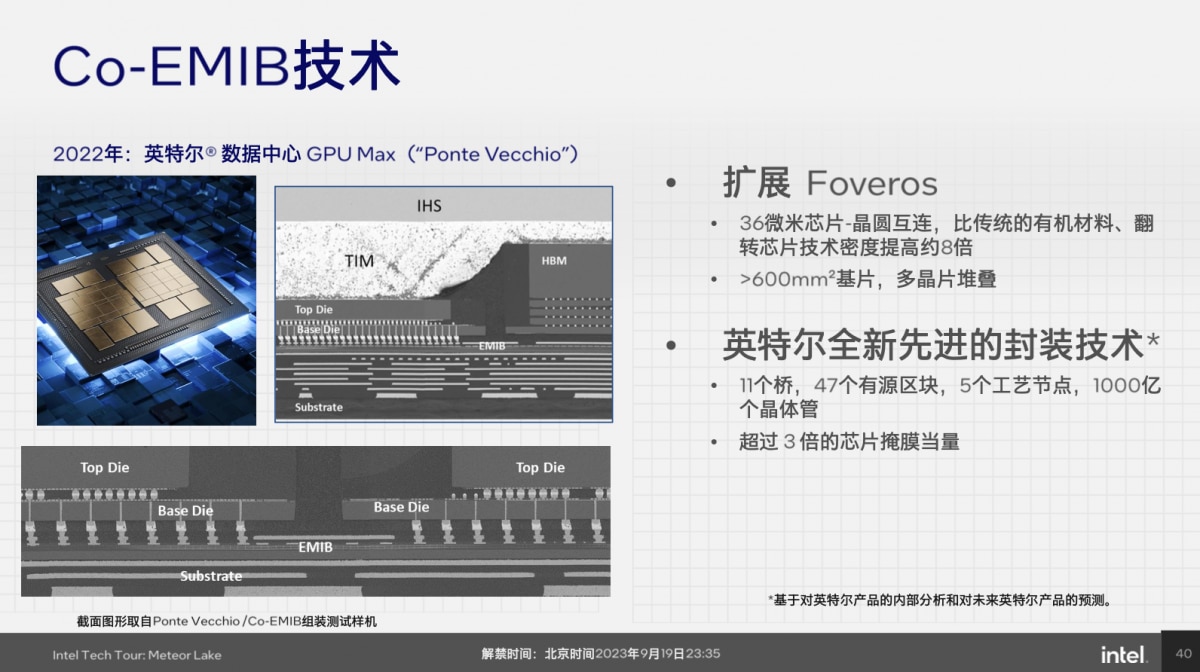

而传说中异常复杂的Ponte Vecchio,也就是2021年Intel Architecture Day上发布的那颗GPU,现在叫GPU Max,则结合了EMIB和Foveros(Intel似乎将其结合命名为Co-EMIB)——即有些地方3D堆叠,水平方向再做2.5D封装。芯片总共包含47个有源tile,采用5种不同的工艺节点。

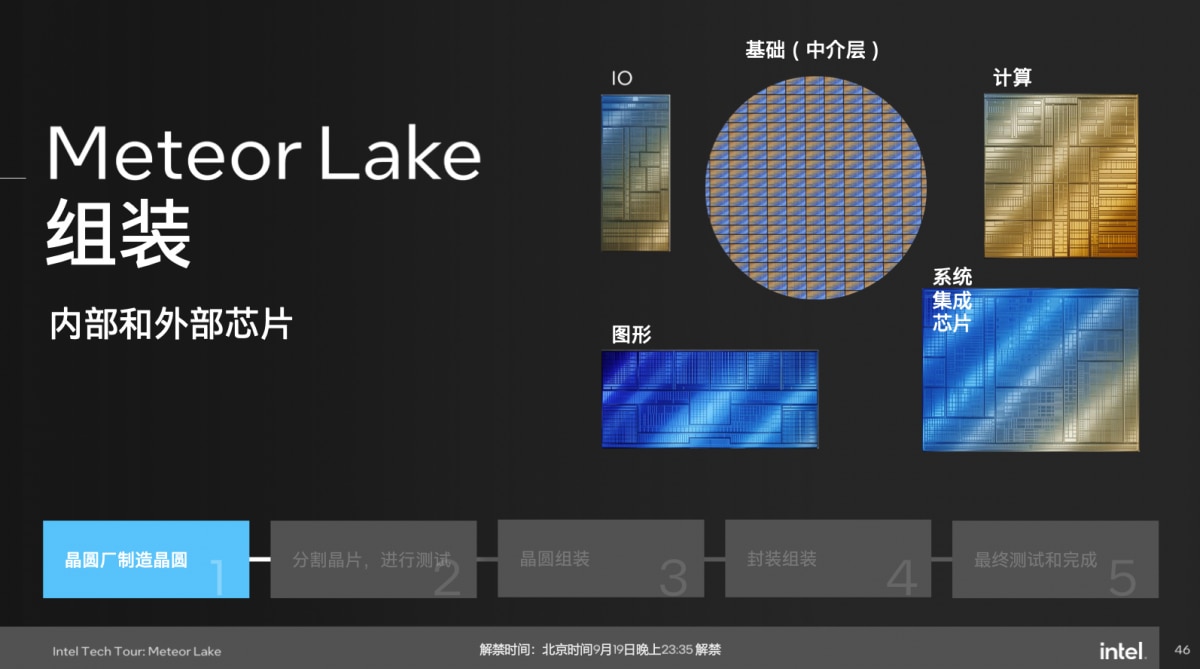

即将上马的Meteor Lake首先是chiplet化的,这一点介绍Meteor Lake技术要点的文章已经谈过。即整颗芯片,是由几片不同的chiplet/die/tile构成的,包括Compute tile、Graphics tile、SoC tile、IO tile;

这些tile又叠在了一片base tile上方。此前传言消息称,其中Compute tile基于Intel 4工艺,base tile则基于Intel 22FFL工艺;还有其他的tile都由台积电制造,但工艺或许也存在差异,包括了N5和N6。

这么做不光是沾了chiplet和先进封装的一切好处——包括不同chiplet可以用最适配的工艺去造、节约成本,从晶圆上切小die提升了晶圆利用率、制造良率;以及更为松散的方案利于规模的弹性化缩放;另一个优势是就产品层面,让不同定位的SKU更容易做,因为不同功能区块都做到了模块化——这一点我们也在Meteor Lake技术要点分享文章里做过解读。

Foveros的真正大规模量产,以及IDM 2.0战略体现的集大成者,应该都在这一代Meteor Lake上。其实看到个人电脑处理器开始大举应用chiplet和先进封装技术,而且明年大概我们就能用上,仍然感觉相当不可思议。抛开隔壁的3D V-Cache应用不谈,Zen的那种chiplet还很难称得上2.5D或3D封装。

所以Intel称Meteor Lake “是40年来最重要的PC架构变化:由monolithic芯片设计,全面转向模块化的设计,3D封装技术则为这种模块化设计提供了最底层的技术支持”。

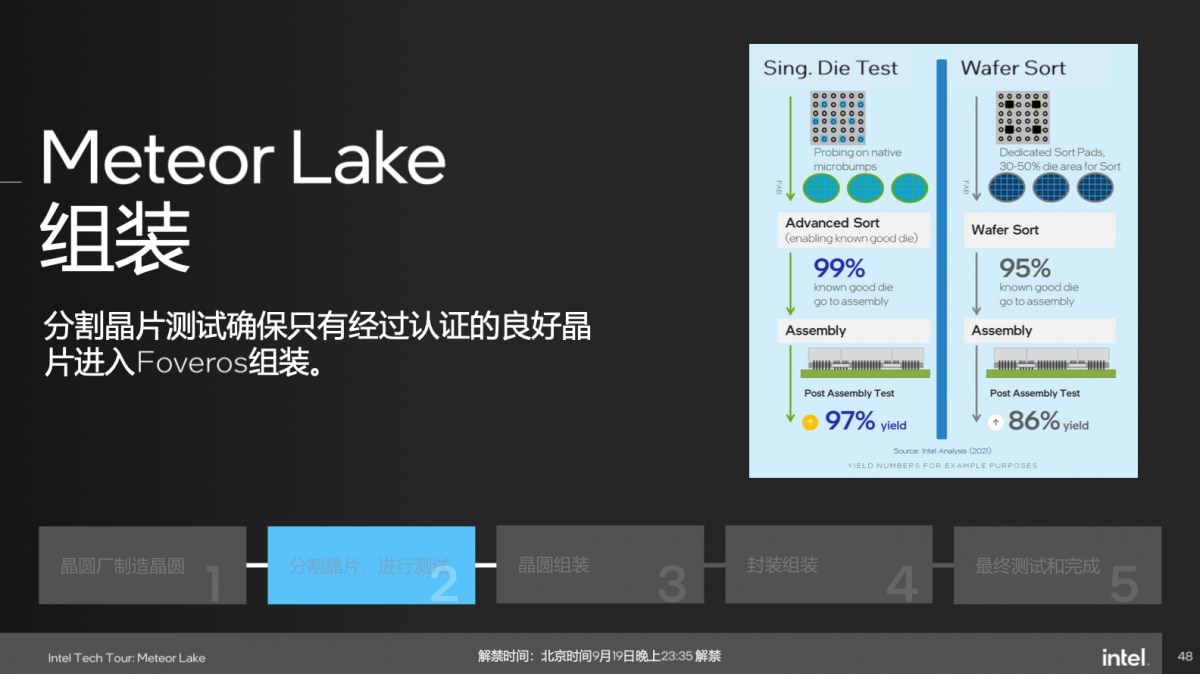

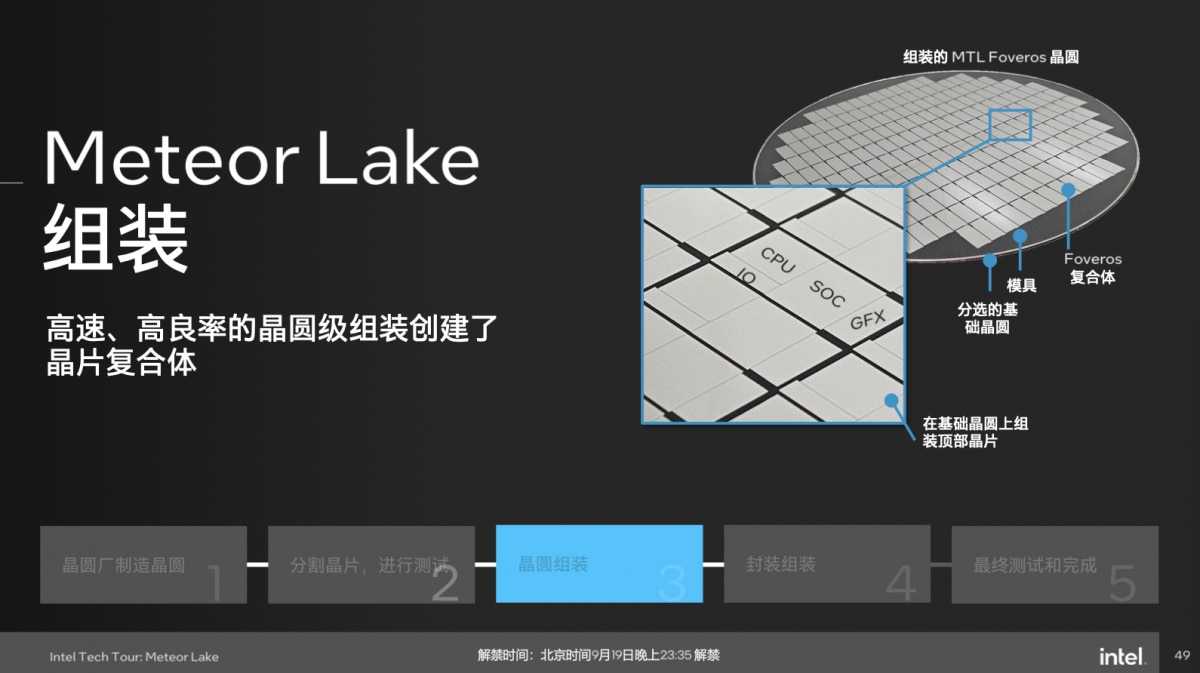

最后分享Meteor Lake“组装”的框架流程,也很有趣,具体如文末的图片。因为Meteor Lake分成了不同的chiplet或tile,所以Intel首先从自家fab厂,以及第三方foundry厂,拿到造好的不同的tile;并做测试。

这些tile要叠到base tile之上。不过base tile晶圆首先是不做切割的。将上述4个tile基于Foveros封装到base tile上。完成堆叠以后,再进行切割与后续封测。

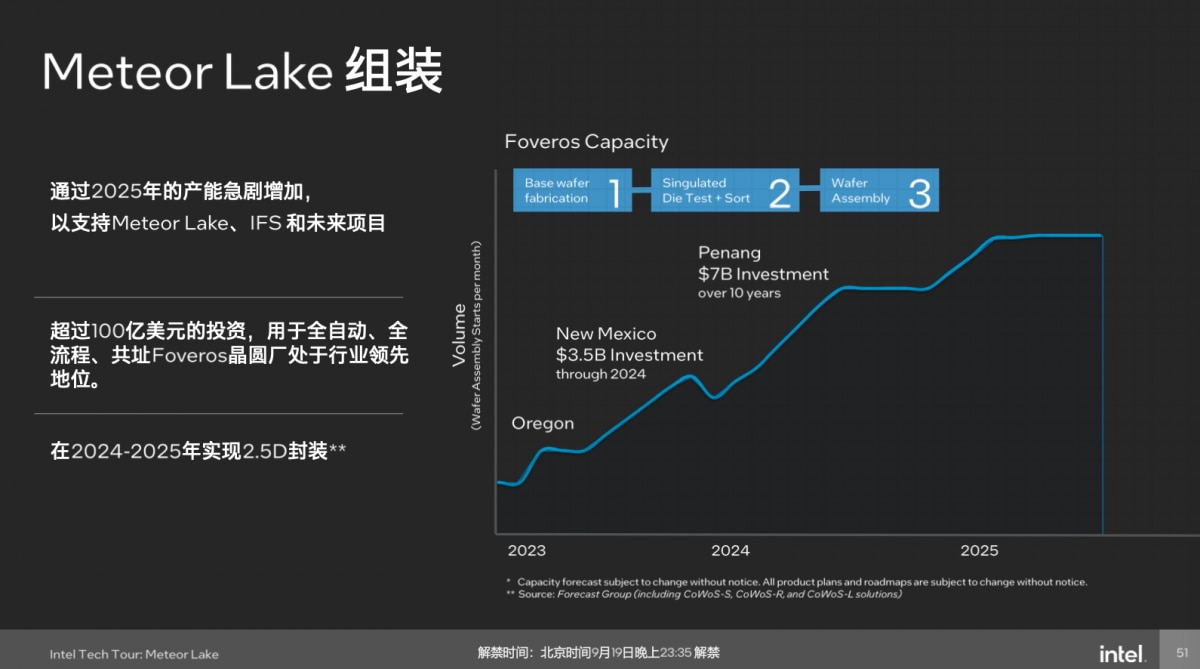

“因为3D封装很复杂,我们也在不断改进封装工厂,加大投资,以配合Meteor Lake以及未来PC产品的生产,以期实现大规模3D封装。”此前Intel就透露过2025年的产能增加计划,以及包括在俄勒冈、新墨西哥和槟城的投资扩产。

眼见PC处理器的新时代很快就要拉开帷幕了。(导读:《马上要来的酷睿Ultra处理器:Meteor Lake关键技术点剖析》《最新的酷睿处理器里面为什么要加一颗NPU?》)

文章来自:https://www.eet-china.com/