随着尺寸的不断微缩,1T1C结构动态随机存储器(DRAM)的存储电容限制问题愈发显著,导致传统1T1C-DRAM面临微缩瓶颈。基于铟镓锌氧(IGZO)晶体管的2T0C-DRAM有望突破1T1C-DRAM的微缩瓶颈,在3D DRAM方面发挥更大的优势。但目前的研究工作都基于平面结构的IGZO器件,形成的2T0C单元尺寸(大约20F2)比相同特征尺寸下的1T1C单元尺寸(6F2)大很多,使IGZO-DRAM缺少密度优势。

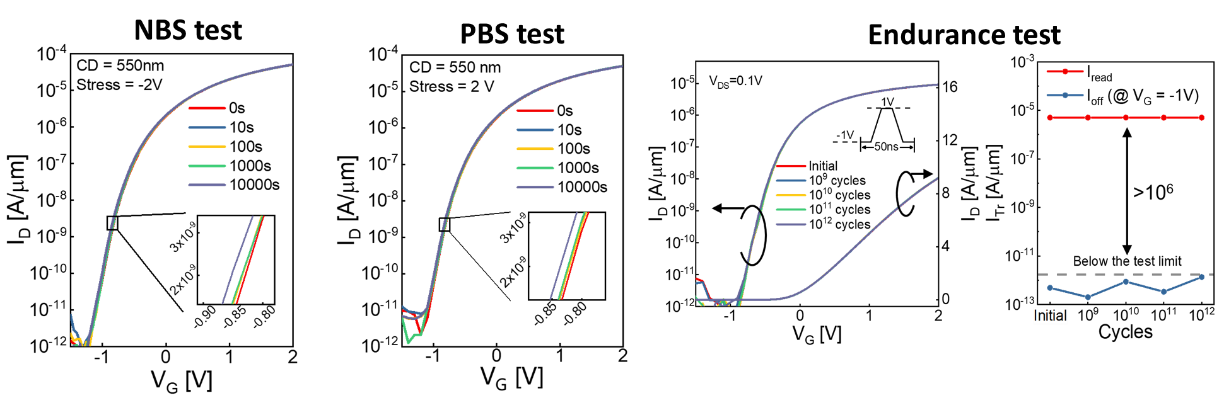

针对平面结构IGZO-DRAM的密度问题,中科院微电子所微电子重点实验室刘明院士团队在垂直环形沟道结构(Channel-All-Around, CAA)IGZO FET 的基础上,研究了第二层器件堆叠前层间介质层工艺的影响,验证了CAA IGZO FET在2T0C DARM应用中的可靠性。经过优化后的IGZO FET表现出优异的可靠性,经过10000秒栅极偏压应力稳定性测试后(包括正偏压与负偏压条件),阈值电压漂移小于25mV,进行1012次写入擦除操作后没有表现出性能劣化。该研究成果有助于推动实现4F2 IGZO 2T0C-DRAM单元。

基于该成果的文章“Inter-Layer Dielectric Engineering for Monolithic Stacking 4F2-2T0C DRAM with Channel-All-Around (CAA) IGZO FET to Achieve Good Reliability (>104s Bias Stress, >1012 Cycles Endurance)”入选2022 IEDM。微电子所硕士生陈传科为名列前茅作者,微电子所李泠研究员、耿玓副研究员为通讯作者。

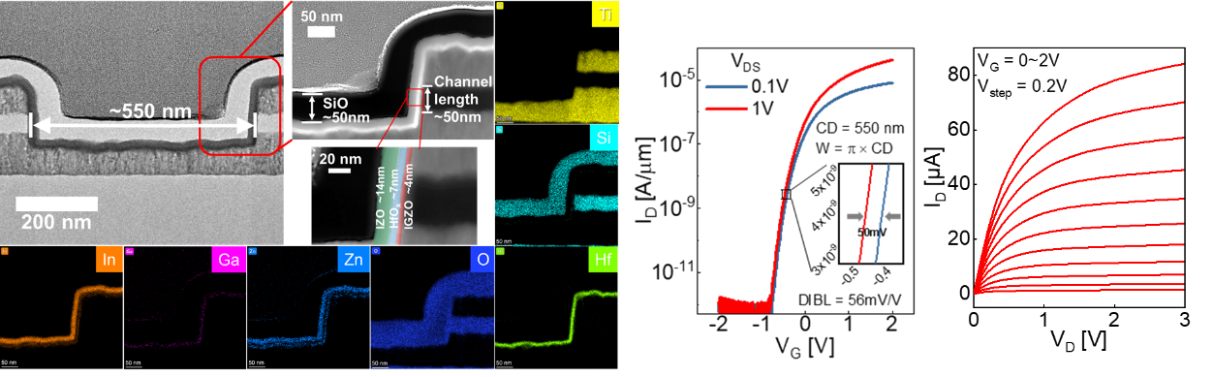

图1, CAA IGZO FET的截面电镜图及转移输出曲线

图2, CAA IGZO FET的可靠性测试结果

文章来自:https://www.eet-china.com/