目前,自旋轨道矩磁阻随机存取存储器(SOT-MRAM)器件在L3存储器应用中面临三个主要问题:可扩展性、动态功耗和制造中对紧凑型无磁场开关解决方案的需求。如今,一次性全面解决这些问题的SOT-MRAM架构已经面世。

近年来,芯片行业对SOT-MRAM技术开发越来越感兴趣。SOT-MRAM是一种很有前途的非易失性存储器,非常适合嵌入式存储器应用,例如高性能计算和移动应用中的L3(及以上)缓存。目前这一角色通常由超快速易失性静态RAM(SRAM)实现,但其对SRAM位密度的工艺升级限制,迫使业界急切寻找替代方案。此外,当存储器待机时,SRAM位元受功耗的影响越来越大,故无法实现很低的待机功耗。而MRAM这样的非易失性存储器,不仅有潜力提供更小的位元,而且其非易失特性也能解决待机功耗问题。

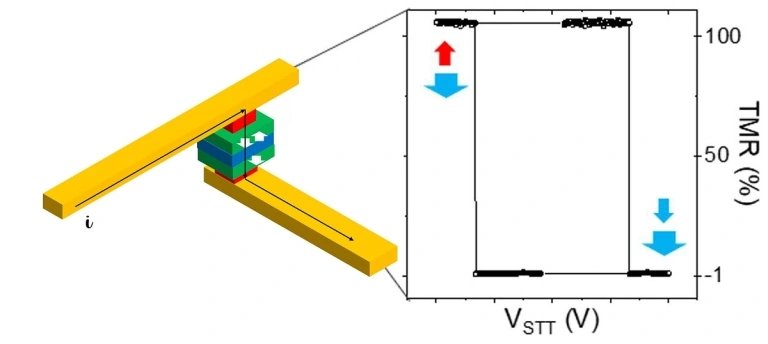

SOT-MRAM是从更成熟的自旋转移矩MRAM(STT-MRAM)演变而来的,由于具有更好的耐久性和两个二进制状态之间更快的切换速度,因此具有更好的缓存应用前景。在两种MRAM类型中,磁隧道结(MTJ)构成了存储单元的“心脏”。在这种MTJ中,薄介电层(MgO)夹在铁磁固定层(CoFeB)和铁磁自由层(CoFe B)之间。存储单元写入是通过切换自由层(即MRAM位元的“存储”层)的磁性来完成的,而读取则是通过电流流过MTJ结来测量MTJ的磁阻来实现的。这种隧道磁阻(TMR)可高可低,取决于自由层和固定层磁性的相对取向(即平行(1)或非平行(0))。

图1:MRAM TMR读取原理示意图。(上部分绿色=固定层(RL);下部分绿色=自由层(FL);蓝色=MgO介电层;i=读取电流)

STT-MRAM和SOT-MRAM之间的主要区别在于写入所用的电流注入几何结构。STT-MRAM中的电流是垂直注入MTJ的,SOT-MRAM的电流注入则发生在平面内,在相邻的SOT层中——典型情况是像钨(W)这样的重金属层。因此SOT-MRAM中的读写路径是去耦的,显著提高了器件的耐久性和读取稳定性。平面型电流注入则消除了STT-MRAM工作时的开关延迟。2018年,imec首次展示了开关速度快至210ps的高可靠性SOT-MRAM,这种器件具有增强的耐久性(>5×1010的开关周期)和300pJ的运行功耗。

由于是非易失性的,SOT-MRAM在高单元密度下可以实现比SRAM低得多的待机功耗。但是由于写入操作需要较大的电流,故动态功耗仍然相对较高。

此外,为了使SOT-MRAM成为嵌入式存储器应用中SRAM的真正竞争对手,需要在提高密度方面进行创新。在固定层和自由层中采用垂直磁化(称为p-MTJ)替代传统的平面型磁化可以提高工艺升级潜力,因为它不再要求存储单元为矩形。

但关键挑战在于器件架构。STT-MRAM采用了柱状结构,是一种双端子器件。当在存储器阵列配置中实现时,每个MTJ单元仅需要一个选择器件(通常是一个(存取)晶体管),来选用于读取或写入的存储元件。具有独立读写路径的SOT-MRAM则是一种三端子器件。在这种情况下,每个存储元件需要两个存取晶体管:一个用于读操作,另一个则用于写操作。因此,独立的读写路径为可靠性提供了额外的好处,但由于需要额外的存取晶体管(附带额外的金属线),它们会占用额外的空间。

还有就是工艺问题。2018年,imec展示了在300mm晶圆上采用CMOS兼容工艺实现全面集成的SOT-MRAM器件模块,极大地促进了工业应用。但是SOT-MRAM p-MTJ位元的实际实现,仍然受到在写操作期间需要额外面内磁场(该磁场主要用来打破对称性并确保确定性的磁性切换)的约束。换句话说,如果没有这个磁场,就不可能知道施加写入电流后自由层的最终状态。在SOT-MRAM开发阶段,该磁场可由外部磁场产生,然而最终还是需要在器件内相应位置产生强磁性的紧致磁场。

到目前为止,针对单个挑战的解决方案都已经得到成功验证,有些解决方案甚至还是在300mm晶圆上得到成功验证的。

外部磁场的作用也可以通过在用于形成SOT层的硬掩模中嵌入铁磁体来实现,从而消除对外部磁场的需要。铁磁体会在磁隧道结的自由层上产生一个小的均匀平面场。2019年,imec证明这种“无场”开关方法是可靠的,同时能维持SOT-MRAM器件的亚纳秒写入速度。

通过采用电压栅极(VG)辅助方法,可以部分缓解与高写入电流有关的问题。在这种VG-SOT-MRAM器件中,SOT效应再次负责切换自由层,实际上的切换是使用平面内电流来实现的。不过如今,受电压控制的磁各向异性(VCMA)栅极可以通过激发电场(穿过隧道势垒)来降低能量势垒而助力其操作。这样一来,写入操作就只需要较小的电流,从而提高了动态功耗性能。

VG辅助方法的另一个优点是它为多柱/多位器件结构打开了大门。与以前一个MTJ支柱连接一个SOT轨道不同,现在可以在共享SOT轨道上实现四个(或更多)MTJ支柱。在这种多柱多位器件中,可以通过在其VCMA栅极上施加电压来选择单个柱(或位)。这样能够减少其能量势垒,从而有利于切换。通过共享SOT轨道只需要一个(大的)存取晶体管(而不是四个)就能完成写入操作,因此总体上位元会更紧凑。

但到目前为止,与多柱操作完全兼容的无磁场解决方案,业界还没有公开展示过。就像上面所述的那样,对于无磁场开关的解决方案,需要在每个p-MTJ柱中嵌入铁磁体,这在很大程度上牺牲了可扩展性。

在IEDM 2022上,imec展示了功能齐全的多柱SOT-MRAM器件,可一次性解决上述所有挑战。

图2:压控VCMA效应和多柱器件示意图。(a)栅极电压调制能量势垒实现切换;(b)能够在多柱器件上进行无磁场操作的混合SOT轨道。

首先,通过在称为混合自旋源的公共SOT轨道内实现平面内磁层,该器件实现了可扩展的无磁场解决方案。这个额外的公共平面内磁层耦合到每个单独的存储单元,它的作用就像对应每个支柱的磁场,但不再是每个单独MTJ堆栈的一部分,从而提高了可扩展性。

其次,VCMA效应通过调制和降低实际开关的能量势垒来辅助写入操作,因而消耗较低的开关能量。

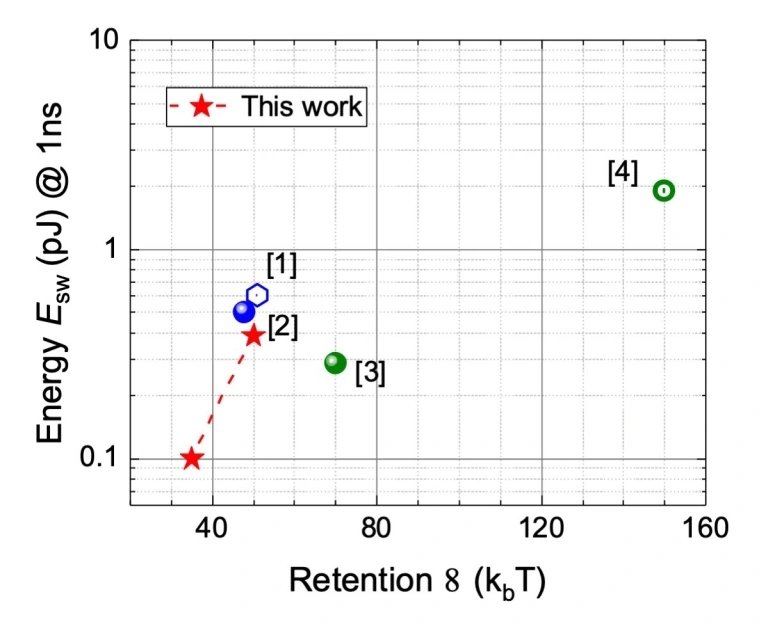

图3:参考和无磁场器件在1ns时的能耗与保持率关系的基准图。采用混合SOT轨道的器件具有与参考样品相当的高SOT效率。

再就是,这种VCMA辅助的概念减少了每位所需的晶体管数量,有利于减小面积占用和提高可扩展性。

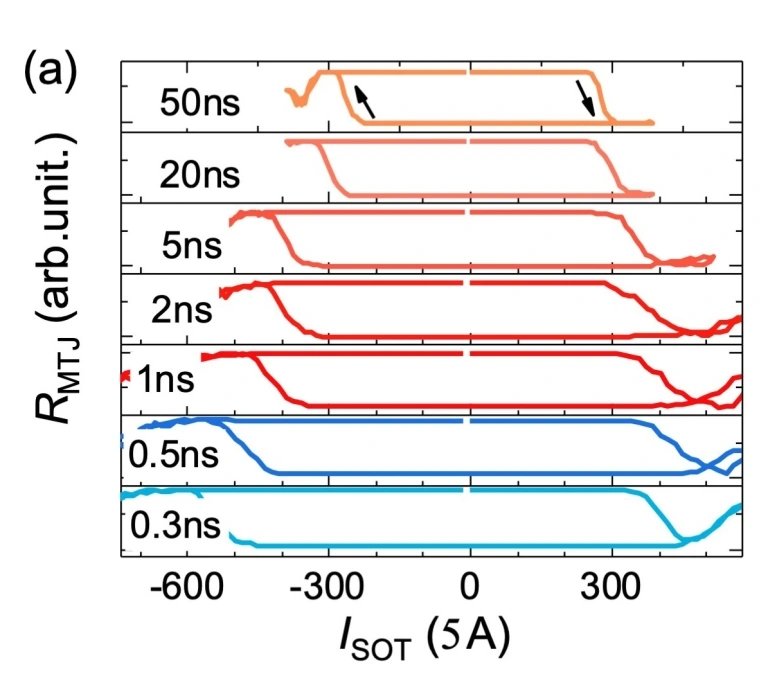

这种器件方案实现了无磁场切换,具有高开关效率(60fJ/bit功耗)、快操作速度(短至300ps)和高耐久性(大于1012)。它适用于单柱和多位SOT器件,而且300mm集成技术兼容CMOS和后端线。

图4:显示了在没有外部磁场的情况下不同脉冲宽度的开关回路图。可以用短至0.3ns的脉冲获得超快速无磁场SOT切换。

上述特性使非易失性SOT-MRAM器件成为高密度末级嵌入式高速缓存应用的可行替代品。

在将这种非易失性SOT-MRAM存储器推向市场之前,还需要完成一些额外的开发工作。当前的工作集中于通过改进SOT轨道和MTJ柱堆叠设计来进一步降低开关能量。此外,imec团队正在致力于SOT-MRAM器件的阵列配置,并将该技术推向工业化。

还可以将SOT-MRAM存储器设想为单独的片外高速缓存芯片的一部分,利用裸片到裸片或裸片到晶片键合技术,将其与逻辑和/或较低级别的高速缓存存储器键合到一起,这在概念上类似于采用3D堆叠式SRAM高速缓存裸片的AMD3D V-cache技术。这种片外解决方案经过在单独裸片上进行优化后,有望比传统的L3嵌入式缓存更具成本效益。

(参考原文:SOT-MRAM Architecture Opens Doors to High-Density Last-Level Cache Memory Applications)

本文为《电子工程专辑》2023年5月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅

文章来自:https://www.eet-china.com/