如何降低芯片功耗目前已经成为半导体产业的热点问题。尤其是近年来,人工智能、5G、大数据中心、汽车等应用带来的IC功能和复杂度呈爆炸性增长态势,使得SoC芯片低功耗设计的重要性与日俱增。传统上对于IC设计企业来说,提高芯片性能最直接的做法就是通过先进的制程工艺来解决,然而,当制程工艺变得越来越先进,单位面积上的晶体管数量成倍增加,即使单个晶体管的功耗随着工艺的进步而降低,但是芯片整体的功耗依然是制约芯片功能的一个重要因素。

清华大学魏少军教授在ICCAD 2022会议上从另外一个角度提出中国IC企业面临的挑战,魏教授指出中国的IC设计已经到了不能仅靠采取更新的工艺来提升产品竞争力的阶段,更多的是需要创新的架构、方法学并配合先进的设计工具来满足产品竞争力的需求。低功耗设计就是其中的一条有效提升产品竞争力的途径,配合创新的架构和设计方法学就有可能在28nm工艺上做出同比14nm性能或更高性能的芯片。

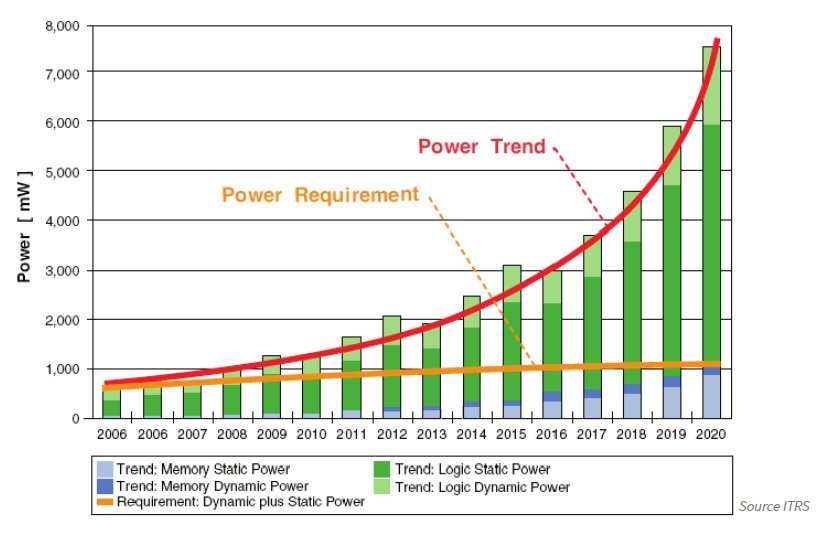

所以不论是从先进工艺IC设计还是成熟节点IC设计,功耗都是IC设计师需要面对和解决的挑战。下图显示了集成电路中功率密度趋势和功率设计需求的对比,随着摩尔定律的演进,集成电路的面积逐步缩小,而其单位面积的功耗不降反升。随着温度的升高,漏电流也会增加,从而导致更大的功耗。据实验显示,温度升高还会导致芯片的平均故障率呈指数上升。通过低功耗设计手段不仅可以实现节能,还可以延长产品寿命。

为了应对这些挑战,设计工程师们运用了各种先进的低功率设计技巧,包括多电压设计、电源关断、动态电压频率调节、自适应电压频率调节、衬底偏置电压调节等。同时,业界还推出了IEEE 1801标准(UPF)来描述功耗设计意图,该标准定义了从RTL到GDS全流程的低功耗管理设计意图,帮助功耗的优化以及相关的设计验证与实现。

事实上,由于低功耗设计方法学的快速迭代,该标准也成为了IEEE变化非常快的标准之一,自2008年名列前茅个版本推出以来,IEEE -1801一共经历了4次大的更新,不同版本之间的兼容性问题使该标准成为EDA领域最难支持的标准之一。

毋庸置疑,在产品成功因素中,面市时间是重要因素之一,有时甚至决定着产品的成败。因此在设计全流程的每一个环节中解决潜在的低功耗问题,对于提高生产率至关重要。

目前的很多设计对逻辑信息来说是“相连的”,因为所有流程都处理逻辑信息,可以自动完成;但对功耗来说可能就是“不相连”的,因为针对每个流程,功耗问题都是独立的,都有它的难度,而且每个阶段所采取的低功耗策略和使用的工具都略有不同,并相互影响。

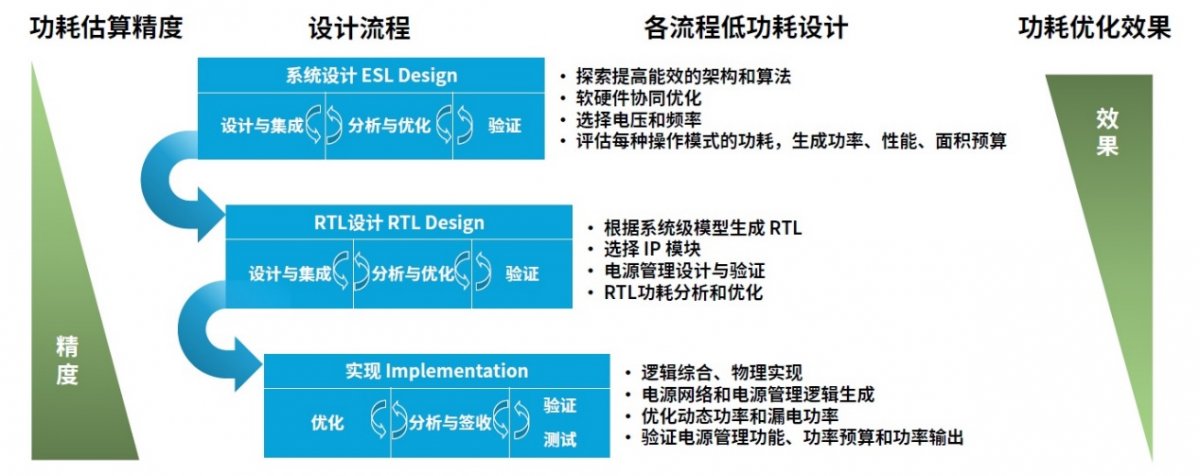

从整个流程看,越早考虑功耗收益越大,但是估算精度往往不够精确。到了设计流程后期,特别是物理实现之后,功耗的估算会更精确,但此时可采用的功耗优化方法与优化的程度都比较有限。

例如早期分析时的难度包括IP模型、逻辑信息、物理信息,需要确认如何去做信息估算的问题;到了逻辑网表阶段,IP模型、逻辑信息都有了,但又缺乏物理信息,“如何确认最后阶段存在的问题是否都得到了处理”,是这个阶段需要解决的问题;可即便是拥有了IP模型、逻辑信息和物理信息,最终的结果也不一定准确,毕竟在每个阶段都需要拿到信号翻转的信息并不是一件容易的事情。

因此,目前在该领域存在“优化效率与估算精度难两全”的困境。对功耗静态分析而言,尽管设计流程早期的功耗估算考虑到了时钟树、关键IP的建模、CPU/GPU/APU的广泛使用、复杂macro IP等因素,但也还要考虑到后端物理实现的影响。这种情况下,芯片工程师需要全面的低功耗设计解决方案,包括兼具速度与精度的功耗分析工具。

EnFortius®“凝锋”低功耗系列EDA软件是英诺达(成都)电子科技有限公司自主研发的系列工具,其名列前茅款Low Power Checker(简称LPC)工具在2022年11月发布,主要用于低功耗设计静态验证,可以为集成电路工程师快速定位低功耗设计所带来的可能的设计漏洞和缺陷。

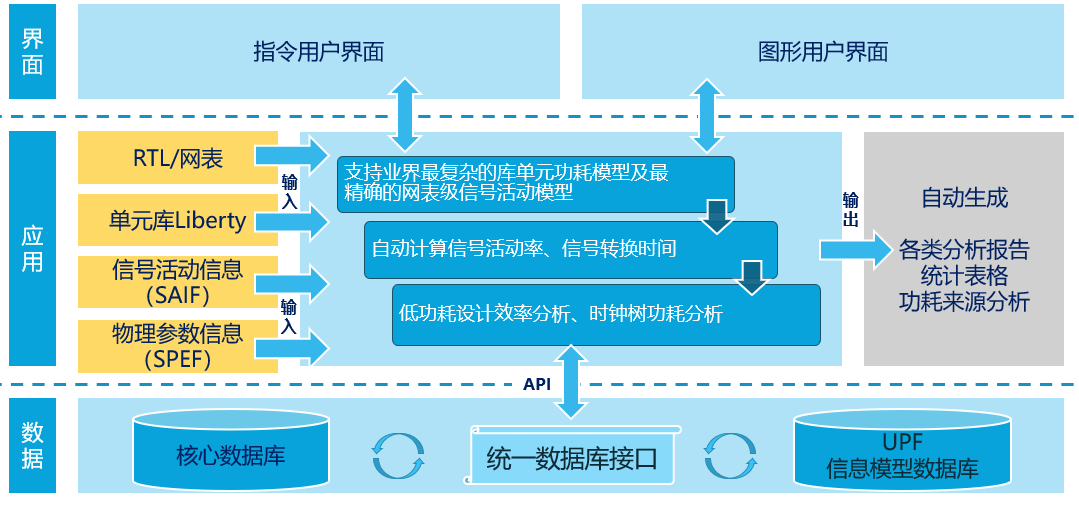

除了低功耗设计验证,另一类常用的就是功耗估算和优化的EDA工具。针对此类需求,英诺达近期推出了一款数字电路门级功耗静态分析工具EnFortius Gate-level Power Analyzer(GPA)。

工具支持工艺库Liberty标准中的各类复杂的漏电功耗和内部功耗模型,以及信号活动文件标准SAIF中的各类信号活动信息,比如更精确描述有源器件的SDPD(state-dependent-path-dependent)信号活动信息,同时工具内建算法可以完成信号活动率、信号转换时间、时钟信号及特殊常量信号在电路中的传导计算,准确快速地完成网表级的功耗分析。配合工具提供的各类报告、电路搜索及查询功能,可以帮助工程师快速有效地定位电路中可能的功耗热点及分析原因,为后续的功耗优化提供数据及解决办法。

EnFortius GPA系统架构图

GPA工具特点:

功耗设计是芯片设计的重要挑战之一,无论是非常先进芯片制程,还是成熟工艺制程,功耗的设计都会是一个很大的挑战。可能很多人对“点工具”存在误解,以为它们只能在设计流程某一个点上做一些小事情。但实际上,低功耗工具是少数贯穿全流程的EDA点工具。

因为IC设计流程的每一步都必须考虑低功耗设计。因此有效的低功耗设计还要求设计团队、IP供应商以及工具和解决方案提供商之间展开密切协作。只有通过实施连贯一致的方法,并将这些方法运用在供应链赖以存在的整个工具领域,电子行业才能真正解决低功率设计所面临的不断增长的挑战。

文章来自:https://www.eet-china.com/