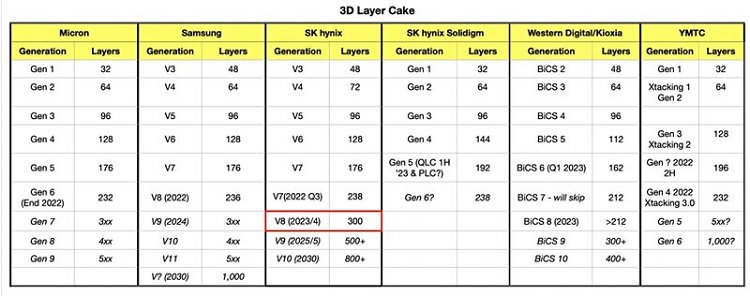

日前,韩国半导体企业SK 海力士(SK-Hynix)宣布,通过 321 层 4D NAND 样品的发布,正式成为业界首家正在开发 300 层以上 NAND 闪存的公司。

在8月8日至10日在圣克拉拉举行的2023闪存峰会(Flash Memory Summit 2023)上,SK 海力士展示了其321层1Tb TLC 4D NAND Flash样品,并透露了开发进展。他们表示,将进一步完善 321 层 NAND 闪存,并计划于 2025 年上半期开始量产。

随着生成型人工智能应用程序(例如由微软公司支持的 OpenAI 开发的 ChatGPT)的快速增长,对能够以更快的速度处理更多数据的先进存储芯片的需求一直在增加。

SK海力士NAND开发负责人Choi Jungdal在大会上发表主题演讲时表示:“随着高性能、大容量NAND的适时推出,我们将努力满足AI时代的要求,持续引领创新。”

他还表示,公司从已经大规模生产的世界较高238层NAND的成功中积累的技术竞争力为321层产品的开发铺平了道路。 “通过另一次突破以解决堆叠限制,SK海力士将开启超过300层的NAND时代并引领市场。”

321 层 1Tb TLC NAND 的效率比上一代 238 层 512Gb 提高了 59%。这是由于数据存储的单元可以以更多的单片数量堆栈至更高,在相同芯片上实现更大存储容量,进而增加了单位晶圆上芯片的产出数量。

实际上,早在今年初的ISSCC 2023会议上,SK海力士就通过一篇论文公布了在3D NAND闪存开发方面的突破,并展示了这款堆叠超过300层的3D NAND闪存原型。

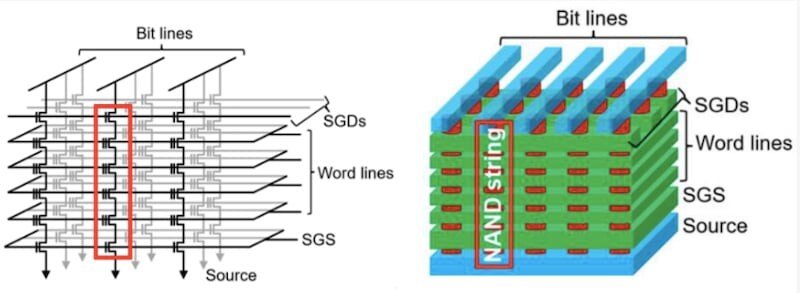

该论文的标题是“高密度存储器和高速接口(High-Density Memories and High-Speed Interface)”,由 35 名 SK 海力士工程师撰写。他们写道,“NAND 闪存领域最重要的主题是持续的性能改进和每比特成本的降低。 为了降低每比特成本,需要增加堆叠层数,同时减小堆叠层之间的间距。 有必要管理因堆叠间距减小而产生的不断增加的 WL(字线)电阻。”

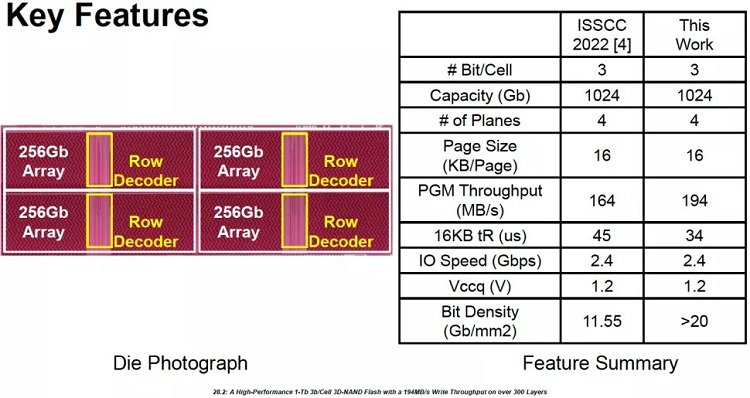

根据当时的介绍,这是SK海力士第8代3D NAND闪存,容量为1Tb(128GB),具有三级单元(TLC)和超过20Gb/mm^2的位密度(bit density)。该芯片的页容量(page size)为16KB,拥有四个planes,接口传输速率为2400MT / s,较高吞吐量为194MB/s(相比第7代238层3D NAND闪存提高了18%)。密度的提升将降低制造过程中每tb的成本,终端消费者最终能从性能和容量的提升中受益。

据SK海力士介绍,第8代3D NAND闪存主要运用了五个方面的技术,包括:

首先,其拥有三重验证程序(TPGM) 功能可缩小单元阈值电压分布,并将 tPROG (编程时间) 减少 10%,从而转化为更高的性能。

其次,采用 Adaptive Unselected String Pre-Charge (AUSP) 技术,再将 tPROG 降低约 2% 。

第三,APR方案可将读取时间降低约 2%,并缩短字线上升时间。

第四,编程虚拟串 (PDS) 技术可藉由降低通道电容负载来缩短 tPROG 和 tR 的界线稳定时间。

最后,平面级读取重试 (PLRR) 功能,允许在不终止其他平面的情况下,更改平面的读取级别。之后,立即发出后续读取命令,并提高服务质量 (QoS),从而提高读取性能。

SK海力士当前的双重验证编程(DPGM)方案将单元分为三组,而TPGM将单元分为四组,因此能够更好地管理其编程(写入)性能。 该论文指出,这“导致程序时间减少了大约 10%”。

此外,SK 海力士还在FMS 2023上推出了针对这些需求而进行优化的下一代 NAND 产品解决方案:采用 PCIe 5 (Gen5) 接口的企业级固态硬盘 (Enterprise SSD, eSSD) 及 UFS 4.0。

SK 海力士还表示,公司在目前积累的产品技术和不断优化企业内部解决方案的基础上,正在积极开发下一代 PCI 6.0 和 UFS 5.0 产品,以致力于在未来继续引领市场。

文章来自:https://www.eet-china.com/