安霸(Ambarella)首席技术官Les Kohn在和《EE Times》的独家访谈中说:“客户一开始都说,我们提供的芯片所支持的‘人工智能’(AI)处理能力过于强大,没有必要。现在,产业对于AI的需求开始暴增。”

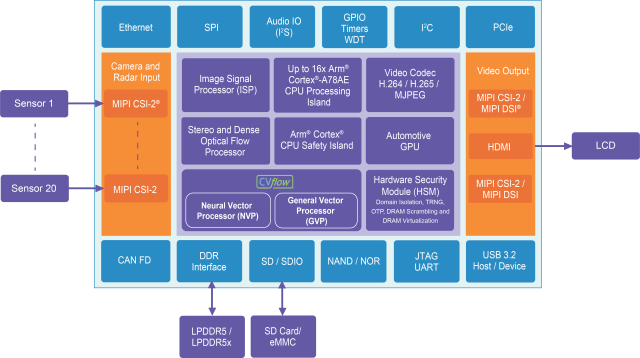

Ambarella的汽车产业客户现在面对再强大的AI运算能力也不嫌多。该公司的CV3系列域控制器主要用于处理L2+到L4级自驾车的感知、多感器融合以及路经规划。CV3系列控制器内建专利的AI加速器,可以同时处理最高20个图像串流。

汽车产业正逐渐朝向域控制器前进,而非在传感器边缘进行AI运算,因为未来自驾车的相机数动辄十台以上,而且还需要加上雷达与其他传感组件。

Ambarella首席技术官Les Kohn在CES 2023上展示产品。(来源:Ambarella)

Kohn表示:“每一个传感器都可能遇到需要进行大量运算的情境,如果全部都要在边缘处理,就必须为每一传感器分配一定资源。其结果是,遇到少数需求量特别庞大的情境,这些资源就不够用。但大多数情境下,资源却反而过剩。”

透过域控制器,可以轻松地在峰值与一般情境之间更均衡地分配处理资源。这也表示,结合不同传感器的原始资料可以实现先进的传感器融合,而无需进行预处理。

Kohn表示:“其结果将更胜于传感器个别处理各自资料,因为若在传感器预处理后才融合资料,很多信息在这时已经遗失了。”

业界对于域控制器的AI处理能力需求不断提高,原因有几个。

尽管旧式的自驾车软件采用传统的算法,透过Arm处理器执行感知、融合以及路径规划。随着AI技术兴起,从感知部份开始,最终涵盖至整个L3级与L4级系统。

Kohn表示,客户还需要预留未来的软件成长空间,包含产品部署后的追加功能。此外,域控制器的高效率AI运算能力也是控制功耗的一种方法。虽然在单相机的系统中,功耗差异不会太大,但到了庞大的L3系统,其功耗差异就可能直接影响电动车的行驶里程。

Kohn补充道,更复杂的L3与L4系统必定需要某种形式的冗余机制,才能符合功能安全的规定。而这也会增加对于AI处理能力的需求。但AI算法本质上就不是100%准确,这要如何和严格的功能安全标准取得平衡呢?

Kohn说:“在我看来,任何L3或L4级的算法,无论基于传统或深度学习技术,都一定会犯错误。就我们目前所看到的,好的深度学习算法发生错误的机率比传统算法来得低。这就是为什么产业开始转向使用深度学习技术。换言之,如果你的目标是实现ASIL-D可靠度,仍然需要一个多样化的系统组合。”

多样化的系统组合可能包含基于传统算法的检查机制。但Kohn认为,最终还是需要两个独立平行的不同深度学习算法。

他说道:“只要它们是完全独立的,就不会同时犯同一种错误。这有助于让你能够实现等同于传统算法的ASIL-D可靠度。”

CV3系列芯片搭载Ambarella自行研发的神经向量运算(NVP)引擎,做为专用的AI加速器,芯片中的其他专用引擎还包含:通用向量处理器(GVP)、图像信号处理器(ISP)、立体视觉与光流运算引擎,以及编码器引擎。这其中是否还有哪些AI工作负载可以进一步独立出来,透过额外的引擎进行处理?

针对这点,Kohn表示:“目前来说言之过早。AI工作的性质如今还在持续变化,若持续导入新的引擎,各种类型的AI运算之间是否能找到合适的平衡可能带来风险。”

Transformer神经网络的视觉应用也在持续成长。CV3系列芯片是最早支持Transformer的特定领域边缘运算加速器。

Kohn说道:“Transformer模型近年来越来越受到关注,尤其是在深度融合相关的应用。因为Transformer目前无疑是结合所有传感器的最佳工具,或至少是其中的关键组件之一。Transformer是现在的潮流。”

安霸的NVP汇集了多项可以降低延迟与提高能源效率的元素。

其中的一项关键是NVP的数据串流编程模型。该模型并非列出低层级指令,而是将卷积或矩阵相乘的高层级运算子(operator)结合为图表,用于描述运算单位间的关联性,以及处理器运算数据的方式。每个运算子之间的通信都在芯片上的存储器完成。这与GPU不同,GPU每一层的数据皆从DRAM读取,完成后再储存为DRAM。Kohn表示,这可以让效率提高十倍以上。

上述NVP中采用的运算子组合是Ambarella努力的成果。该公司在“算法优先”的原则下研究客户的神经网络与传统算法,针对其打造优化的演算子组合,并进一步针对这些演算子设计优化的数据路径。

CV3系列芯片针对AI 、向量运算、图像运算、立体视觉与光流运算,以及编码器引擎等领域提供其专用的加速引擎。(来源:Ambarella)

Kohn表示,另一个对效能有贡献的技术是“稀疏运算”(sparse processing),不论是对矩阵或卷积相乘都相当重要。

他说:“很多厂商宣称支持稀疏运算,但实际上提供的是结构化剪枝(structured pruning)。简单来说,就是砍掉网络中的部份通道,因而改变了网络的结构。相形之下,稀疏运算的做法是,你可以将例如每四个系数中的两个设为零,但这仍然有其局限性。当你的稀疏运算存在这么多限制,对于准确性就会有很大的影响。”

Ambarella的设计支持随机稀疏运算:任何位置的任何权重都可以为零,如果超过一半的权重为零,就不需处理其余部份(采用其他机制仍需要处理四个零中的两个)。

由于具备这种灵活性,让Ambarella的技术比竞争对手的方案更有效地将网络稀疏化(缩减大小),并提升整体网络速度,因为需要的运算量减少了。然而,这种方法需要一个反复训练的过程,透过渐进式的稀疏化,将准确性提升到极限。透过Ambarella的工具链在每一个步骤反复训练,准确性的损耗可以被降到最小。

相较于NVP,独立的通用向量处理器(GVP)主要任务是雷达处理算法。然而,Kohn表示,若未涉及大量使用卷积与矩阵相乘的工作负载,在GVP运行的速度相当于NVP,而且由于其晶粒体积较小,因而能源效率更佳。

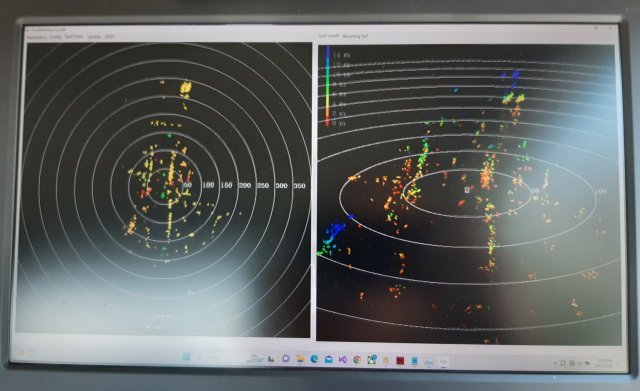

Ambarella为《EE Times 》现场展示其雷达技术。(来源:EE Times)

CV3的NVP加速器支持16位、8位以及4位的精准度。Kohn过去曾告诉《EE Times》,混合精度应该是最实际的解决方案,但再那之后我们仅看到少数几个8位以下的边缘应用案例。

他说道:“除了超低功耗的嵌入式应用,要做到8位以下的更复杂应用非常困难。其中难度特别高的部分在于启动数据。如果将权重压缩到8位以下会比较简单,而实际上,我们已经在某些案例这么做了。为了在复杂的网络中将启动数据压到8位以下,意味着很难维持准确性。”

Kohn表示,4位权重可以有效改善存储区宽带,并在某些情境下改善效能。某些分层甚至可以在纯粹的4位下运行,而有些分层至少要达到16位启动。

Ambarella的工具可以自动处理混合精度量化。

Kohn表示:“一切都取决于是否有好的训练数据。我们会有一个量化版本是不需要任何重复训练,只需要一些校准数据。这么做的速度更快。但如果你想要尝试极限,仍然需要量化感知的重复训练。”

Kohn在1980年代曾经担任英特尔(Intel)首款RISC芯片i860的首席架构师,长期以来大力推崇RISC。CV3系列目前搭载Arm核心。因此,我们问Kohn认为是否有一天会在Ambarella旗下产品中采纳RISC-V核心?

他回答道:“我们确实曾经思考过。但这必须在效能上与高端Arm处理器竞争,并同时符合功能安全的需求,这是一大难题。相关的技术还没有到位。除此之外,我们的客户是否会接受也是个问题。”

他表示,汽车产业的客户对于采用新架构往往抱持较保守的态度。Ambarella内部拥有基于OpenRISC (早于RISC-V)的核心设计,有机会改造为RISC-V。Kohn说道:“如果我们能为主处理器和芯片上的其他组件提供一个通用的架构,那就是一大成就。”

Kohn进一步表示,为了满足客户日与俱增的需求,Ambarella的未来发展蓝图是开发更大、更快且更高效的芯片。针对L2和L2+的应用,Ambarella仍会推出成本效益较高的小芯片。但针对广大的L4操作适用范围(ODD),Kohn认为:“势必需要用到多个高效能的强大芯片。”

(参考原文:Les Kohn: ‘L4 Will Need Multiple Big Chips’,by Sally Ward-Foxton)

文章来自:https://www.eet-china.com/