半导体产业整体发展状况的风向标,自然就是存储芯片了。过去我们最常聊的还是NAND,而和NAND存在强周期关联性的是DRAM——虽然这两者的周期并不完全一致,但这两者的上下行周期前后脚的关系是不变的。

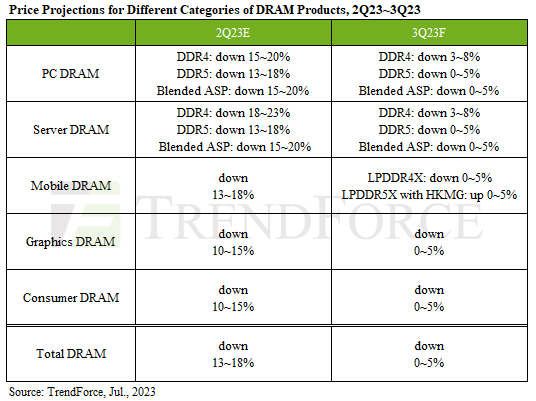

不出所料的是,当前产业下行期内,DRAM和NAND价格下跌还在持续。TrendForce今年7月份的报告显示,DRAM供应商供给仍然出现季度环比递减——库存水位还是很高,让DRAM价格仍处在低位。TrendForce预计今年Q3,DRAM的ASP(Average Sale Price)还将总体下跌0-5%。虽说上游收缩生产规模会缓解价格压力,但价格反弹至少需要等到2024年。

受到季节性需求量增加的影响,从TrendForce给出不同领域的DRAM价格环比下跌幅度来看,下跌幅度在收窄。其中还是看到一些市场有恢复迹象的信号,比如移动DRAM,持续性的价格下跌基本达到了供应商所能承受的基准线,某些供应商的移动DRAM产品价格偶有小幅反弹,虽然下行通道仍未完全触底。

市场的这种周期性变化终将结束,新一波上扬前就要看现存市场参与者在这段沉默期的积累情况了。国内我们也看到一些新兴企业的逐步发力,比如东芯半导体,不仅是DDR产品在通讯设备、移动终端等领域应用的布局,还有LPDDR系列也在扩大布局:除了已经比较成熟的LPDDR1和LPDDR2系列,东芯去年的年报还提到,公司在研的LPDDR4X产品已为客户提供样品,可用于基带市场和模块类客户。

东芯2022年报在研项目列表中也提到了25nm 4Gb LPDDR4X,这一阶段的投资规模在2800万元。今年7月,东芯股份披露最新调研纪要,提到目前公司自主设计研发的LPDDR4X产品已经提供样品给客户进行测试,导入进度符合预期。虽然从年报来看,DRAM业务营收8162.50万元,只占到东芯总营收的大约7%,和NAND业务规模相去甚远,DRAM却也是行业未来不可或缺,国产市场极为重要的存储产品类型。

既然LPDDR4X未来还将为东芯等市场参与者开启更为广阔的市场,这篇文章我们就从LPDDR技术的历史,来谈谈这项LP(low power)低功耗技术的过去和将来。

LPDDR的“LP”就是指低功耗,从名称来看就知道是相较于DDR更低功耗的SDRAM类型产品,当然也是扮演内存角色——从维基百科的介绍来看,LPDDR较早就叫Mobile DDR或mDDR,毕竟其最初主打的市场都在移动设备。

LPDDR标准诞生的时间比很多人要想象得晚,虽然具体的年份现在很难查到,但大约就在2008年前后。当讨论手机的主内存系统时,90年代后期的手机普遍在用EDO DRAM(Extended Data Out DRAM)——这种DRAM芯片主要是用于提升FPM DRAM(Fast Page Mode)的性能而生的。

2007年iPhone初代问世,应用的也都还不是LPDDR内存。iPhone初代采用的是eDRAM(embedded DRAM)——就仅有来自TechInsights的归档历史资料来看,iPhone一代采用的AP SoC是三星S5L8900,其中有eDRAM——和AP一起做PoP(Package on Package)封装,是叠起来的512Mb三星DRAM颗粒。

随后mDDR/LPDDR初代才真正到来。较早的LPDDR是DDR的改款,主要的变化都着力在降低总体功耗上——其中最大的变化就是将VDDQ电压(输出到内存芯片buffer的供电电压)从2.5V降低到了1.8V——这自然就是“LP”低功耗属性的体现了。

另外,因为初衷就在面向功耗敏感型设备,自然还会融入一些节能特性,比如说Deep Power Down Mode(用于休眠状态下大幅降低功耗)、可配置自刷新与温度补偿自刷新(temperature-compensated self-refresh,降低刷新数来降低功耗)等。

在数据位宽方面,DDR一般为64bit,LPDDR缩减到32bit——制造商也可以按照需要选择16bit甚至是8bit。其他主要的基础配置都来自于同代DDR,包括2n预取大小(prefetech size),内部时钟频率200-266MHz,数据传输速率通常400MT/s-533MT/s。

较早期的LPDDR规格很不统一,2008年末JEDEC针对LPDDR发布了JESD209B,如此LPDDR也就归入到JEDEC标准管理,成为行业的统一标准。比较知名采用了LPDDR初代规格的移动设备包括有iPhone 3GS、初代iPad、摩托罗拉Droid X等。

参照东芯半导体的资料,其目前在售的LPDDR1系列产品有512Mb、1Gb、2Gb不同密度颗粒可选,电压1.8V,166MHz/200MHz频率,FBGA 60/90ball,线宽x16/x32规格。

值得一提的是,东芯有一类型的产品名为MCP(Multi Chip Package,多芯片封装存储器)——这是一种结合了非易失性代码型闪存与易失性存储芯片两者的产品,是将其NAND闪存与LPDDR做组合——因为都采用低电压设计,所以DRAM部分用的都是LPDDR。

官网可看到的产品,选择LPDDR1的一款型号FMN1SD5SBB-50IA,LPDDR部分是512Mb(3M x16 x4Bank)200MHz规格,FBGA 130(8 x 9 x 1.0mm)封装;且运行环境温度达到工业标准的-40~85℃。产品介绍的低功耗特性里,也明确标注着低功耗供电、Auto TCSR(自动温度补偿自刷新)、PASR(局部阵列自刷新)节电模式、Deep Power Down Mode、DS(Driver Strength)控制等。

这类产品主要面向移动互联网与IoT应用。东芯在财报中说,使用NAND MCP产品可以减小PCB的布板空间,降低整体系统成本,提高整体集成度和可靠性,适用于PCB布板空间狭小的应用。虽然前文提到DRAM产品目前在东芯的整体营收中所占份额仅有约7%,但2022年MCP类产品营收2.2534亿元人民币,占到总营收的将近20%——可能对东芯而言,LPDDR产品的价值更大地发挥在了这一部分。

内存作为处理器周边最为重要的存储器件之一,必然是要随着处理器速度的加快而做出同步更新换代的,因为更快的数据处理或控制速度,必然意味着对存储有着更高的读写速度与更大的容量要求。大部分人对于DDR和LPDDR的每次迭代,首先能想到的应该就是传输速率,以及密度与容量的加大。

实际上并不止于此,尤其LPDDR在后续的发展里变得更为独立。2009年,JEDEC发布JESD209-2,定义了全新的低功耗DDR接口标准。除了增加存储密度、提升性能、降低功耗、减小封装尺寸,LPDDR2和DDR1、DDR2都不再兼容;而且LPDDR2还包含非易失性存储接口标准。

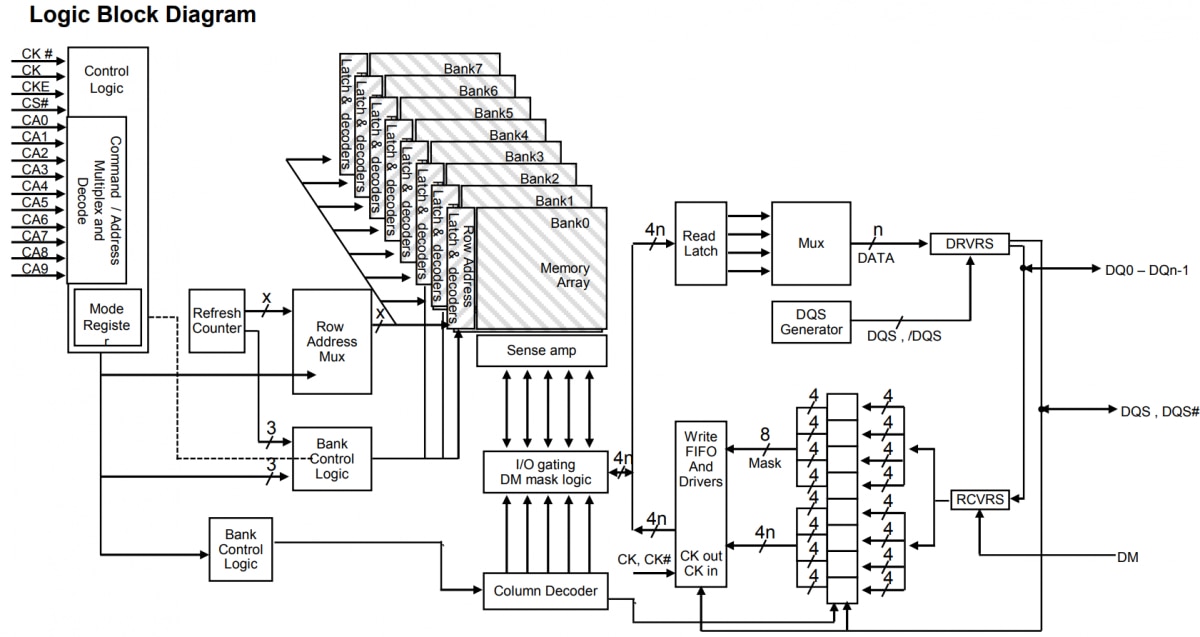

实际上LPDDR2分成了LPDDR2-S2、LPDDR2-S4,和LPDDR2-N。后者就是非易失性存储类别——LPDDR2应该算是首次达成了闪存与SDRAM接口共享——对于存储子系统而言,降低了控制器pin数、增加了密度;前两者分别在预取规格上是2n和4n。当然LPDDR2将传输速率提高到了最大1066MT/s(最大533MHz频率),若选择32bit位宽,带宽总体增加到了4.2GB/s,比前代达成了翻番;存储密度较高也达到8Gb,电压降到1.2V则进一步实现了能效提升。

节电特性方面,其低功耗状态和LPDDR初代类似,额外增加了一些“PASR(Partial Array Self Refresh,局部阵列自刷新)”选项,以及“按照Bank刷新(Per-Bank Refresh)”等特性更新;

关注IoT的读者应该知道LPDDR2的寿命是比较久的,现在的应用仍然相当广泛。东芯的LPDDR2产品列表中涵盖密度1Gb、2Gb、4Gb的产品,运行电压1.8V/1.2V两种规格,I/O总线频率400MHz/533MHz,线宽x16/x32,134-ball FBGA封装;

东芯的MCP类型产品基于LPDDR2的就比较多了,这可能和LPDDR2标准本身的特性有关。其中较高规格的FMN2ET4DCF-25IH的LPDDR2部分是4Gb容量密度(16M x 32 x 8 Banks),400MHz频率,162-ball FBGA封装(8 x 10.5 x 11mm)。另外这颗芯片的LPDDR2部分,也基于LPDDR2规格新增的多路复用控制与地址线到10bit双数据速率DDR CA总线上,减少了系统的输入pin总数;并且做到4n预取。

多提一句,因为本文只关注LPDDR,所以未曾涉及MCP芯片的NAND闪存部分——这部分也是东芯半导体的核心技术构成要件。

LPDDR2再往后走自然就是LPDDR3了——这一代JESD209-3低功耗内存设备标准规格发布于2012年5月。当然LPDDR3提供更高的数据速率1600MT/s(LPDDR3e达到了2133MT/s)、更大的带宽、更优的能效和存储密度——尤其存储密度较高提升到了32Gb。LPDDR3也引入了一些新的技术,如Writing Leveling(写入均衡)、CA Training Mode训练模式、ODT(on-die termination,die上终端电阻)、低IO电容等。

LPDDR3不再包含闪存指令,且限定8n预取规格;LPDDR3对于PoP或独立封装的原生支持,吸引了不少移动领域的设备采用。加上规格进步对于1080p视频播放需求的满足,这一代也就让LPDDR技术在移动和消费设备上变得名声大噪,iPhone 5s、MacBook Air、Surface Pro 3/4都采用LPDDR3,高通骁龙600/800对于LPDDR3e的支持也让LPDDR成为移动市场当仁不让的内存标准。

JEDEC早于2012年3月召开会议探讨LPDDR4新标准,到2014年8月才正式发布了JESD209-4 LPDDR4低功耗内存设备标准。这期间移动市场的多媒体类应用对内存带宽需求提高了不少,移动计算及对应功耗、带宽的平衡需要新标准乃至新架构。

LPDDR4主要改进包括接口速度翻番,外加一些对应的变化,比如把IO标准改成了LVSTL( low-voltage swing-terminated logic);达成了更小的运行电压,从此前的1.2V降低到1.1V;另一方面预取大小转向16n,相比前代再翻了一番,也就是说即便不增加内部时钟频率,也能提升带宽;与此同时,内部总线从32bit转变为2 x16bit——类似于双通道,提升访问效率、降低功耗——每个通道能连接封装内的非常多2片die。

另外,前文多次提到的CA总线由10bit DDR双数据速率,在LPDDR4上变成了6bit SDR单数据速率总线——但增加了多周期指令功能,实际上频率更高,burst长度(BL,有资料将其译作突发长度,即连续读几个列地址)更长,控制信号也就能够实现更进一步的多路复用——SDR和更窄的位宽都是为了降低能耗。据说相比于4Gb LPDDR3颗粒封装的2GB内存,用8Gb LPDDR4颗粒同样做个2GB内存,能节约非常多40%的功耗。

其他改进还包括专用指令用于自刷新,封装尺寸进一步减小,存储密度增加等。LPDDR4带宽翻番,规格上全面达成对UHD也就是4K影像播放、拍摄的支持,自然也推动了LPDDR4的快速普及。

这一代尤为值得一提的是LPDDR4X——这一版迭代标准最惊艳之处是将VDDQ从1.1V降到了0.6V,降幅差不多有近50%。即便就系统层面来看,需要增加新的电压I/O供电成本,这么大幅度的节能也能值回票价。与此同时LPDDR4X通过增加终端电阻(termination)与校准选项,规格上的最大传输速率提升至4266MT/s。

除了更低的电压,其他变化还包括对于更小型的应用有单通道die选择,还有新的MCP、PoP与IoT封装方式等支持。JEDEC有发布两个相关LPDDR4的标准,基础标准LESD209-4就包含了LPDDR4和LPDDR4X的信息;另一个是JESD209-4-1,作为附加项主要就是描述LPDDR4X相比于LPDDR4的差异和增减的。

DRAM市场上,LPDDR4(X)产品显然是被东芯寄予了厚望的。6月份,东芯还发表了一篇题为《DRAM产品低功耗设计与演化》的文章,谈到DDR3、DDR4和LPDDR4(X)产品的差异,论及DDR3到LPDDR4接口设计变化,有兴趣的读者可以前往看一看——其中特别提到“东芯半导体的DRAM产品都是符合国际接口规范的产品,替换无压力”。

目前我们已经能够从东芯半导体的官网看到LPDDR4(X),不过现有信息仍然不多:包括1Gb/2Gb密度——4Gb颗粒尚未出现,电压1.1V/0.6V不同规格,频率1600MHz/1866MHz/2133MHz几种,200-ball FBGA封装,x16/x32线宽。

去年年报上,东芯对于25nm 4Gb LPDDR4X的应用定位是“高端数据模块”——既然已经送样,那么离正式与我们见面应当也不远。“公司在研的LPDDR4X以及PSRAM产品均已为客户提供样品,可用于基带市场和模块类客户”;这里PSRAM(伪静态SRAM存储器)暂且不提,modem和模块对于DRAM的需求自然是理所应当的。

当然,现在移动设备主内存开始出现LPDDR5、LPDDR5X。主要改进再次为增加数据传输速率,且采用差分时钟,bank数量增加到16个——分成4个bank groups,节能方面多了Data-Copy和Write-X指令以及引入DVFS(动态频率与电压调节),加入新的时钟架构WCK与RDQS;LPDDR5X进一步做了速度扩展,另外有可靠性、信号完整性方面的加强,包括link ECC特性引入。

LPDDR5很显然是为达成移动设备更高性能而设的,所以架构标准做了重新设计。东芯暂时还没有出LPDDR5标准的DRAM产品,所以这里不做过多讨论。

虽然市场上没有特别针对LPDDR做研究的报告,不过如文首所述,存储芯片可以看做是电子产业的风向标:LPDDR作为存储芯片的一个类别,而且以移动与IoT这类大容量市场为目标,自然是整个行业发展方向的写照。

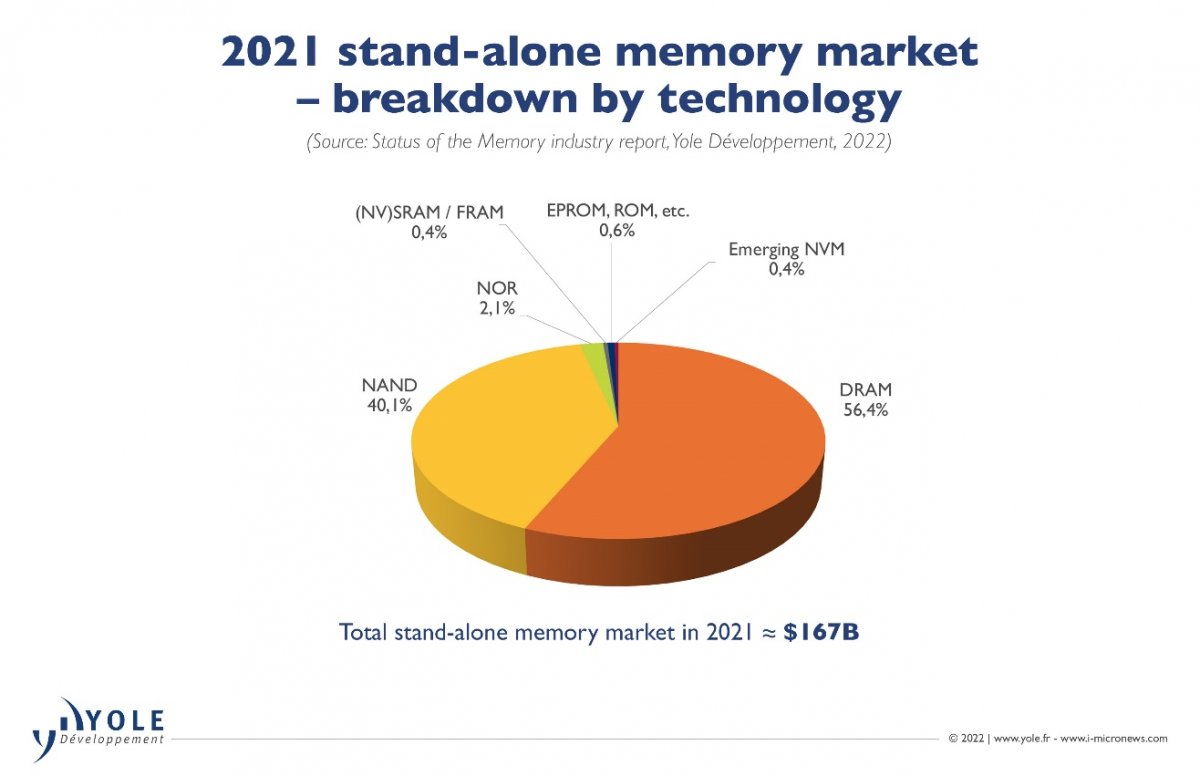

而且DRAM本身也是存储芯片市场最大的组成部分(2021年的数据为56.4%)。Yole Intelligence去年给出的数据是,预计到2027年DRAM市场价值会超过1500亿美元,2021-2027的CAGR年复合增长率为9%——虽然这中间会存在周期性变化。那么很显然DDR、LPDDR、MCP这样的产品对于东芯半导体未来的营收增长也会起到越来越关键的作用。

文章来自:https://www.eet-china.com/