过去几年,半导体行业在不确定的环境下依然实现了确定的增长。人工智能、5G 通信、超大规模计算、自动驾驶和工业物联网等技术不断驱动着新一代产品的设计活动。在此趋势下,芯片和系统设计的复杂性也不断增加,如何利用人工智能/机器学习,实现更多自动化来提升设计效率将成为成功的关键。

Cadence 作为全球 EDA 产业的先进企业,致力于人工智能的研发。公司对于面向下一个世代的 EDA 目标是将传统的单一工具和单一运行环境转变为多运行、多工具协作的设计环境,并结合大数据平台和强化学习从设计数据中学习,从而能够为下一次 EDA 工具运行自动做出优化决策。这样可以大量减少人工决策和 debug 的时间,从而将工程师的生产力提升数十倍。

“迄今为止,Cadence 拥有最全面的人工智能驱动设计平台产品组合,涵盖从芯片到系统的各个领域。Cadence 正在利用我们的计算软件专业知识,为跨多个垂直领域的客户提供创新解决方案,我们致力于用 EDA 和 IP,助力自动化电子设计从概念成为现实。”日前,在上海浦东嘉里大酒店举办的CadenceLIVE China 2023 中国用户大会上,Cadence资深副总裁兼数字与签核事业部总经理 滕晋庆博士 在接受《电子工程专辑》等媒体采访时说到。

Cadence资深副总裁兼数字与签核事业部总经理 滕晋庆博士

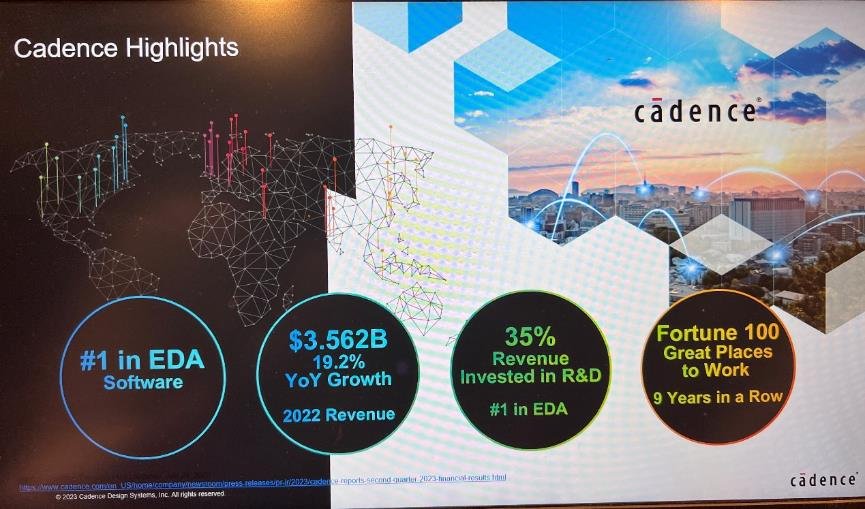

据介绍,Cadence共有四大事业部,分别是模拟与PCB(Analog & PCB)、数字与签核(Digital & Signoff)、验证(Verification)以及IP。四个事业部在过去几年发展良好,让整个Cadence业绩在2022年实现了约20%的增长,其中EDA软件部分贡献最大。

“你会发现,目前在做3纳米和5纳米工艺芯片的厂商,60-70%都在用Cadence 布局布线工具。” 滕晋庆说到,另外在中国市场中80%做P&R (Place and Route)工作都是用Cadence的Innovus工具。“我们对此非常自豪,当然也还有很多努力的空间。”

在本次采访中,滕晋庆还就EDA工具向系统级和半导体产业之外的延伸、降低能耗、3D-IC与Chiplet、汽车半导体以及人工智能等方面的应用做了详细的阐述。

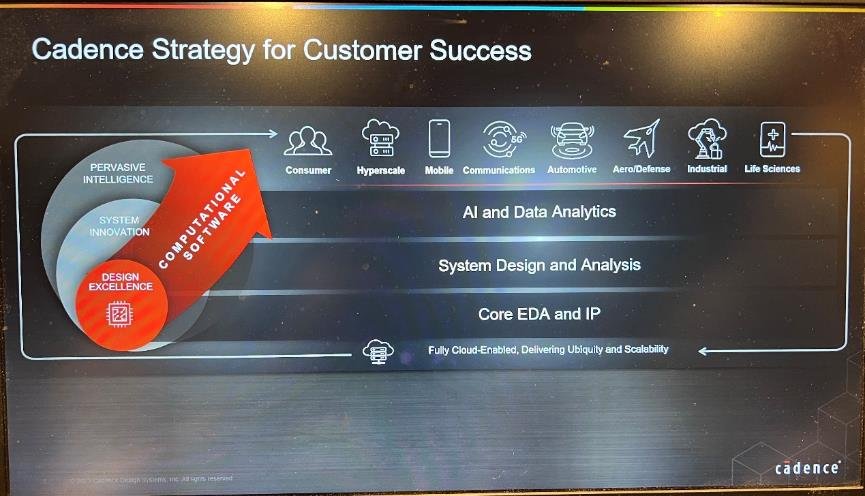

EDA公司的专长一直以来就是计算软件(computational software),Cadence也不例外,其深度的内核技术就是计算科学与数学。这类知识可以被充分运用在芯片设计以及很多其他领域中,例如系统级设计与分析中的三维电磁场仿真、三维热仿真、计算流体力学(CFD)等。

过去,Cadence公司给人的印象就是主营EDA工具和IP,而如今他们新的策略已经变为智能系统设计(intelligent system design),将业务范围延伸到系统级别、AI,甚至生物制药方面,例如把计算软件上的优势用在药物分子研究上。

滕晋庆表示,药物分子仿真对药物分析非常重要。“以前这个领域的人了解分子和模型,可是不知道怎么把这些仿真做得更好更快,结合我们的计算软件可以做到。”

两年前,Cadence收购了计算分子设计的行业领导者OpenEye Scientific Software, Inc.(OpenEye)公司,其产品被制药和生物技术公司用于新药研发。全球排名前20的制药公司中有19家是OpenEye的客户,包括辉瑞和阿斯利康。

除了医药领域,AI加持的EDA工具也在系统设计(system design)上大展拳脚。回顾1990年代读博期间,滕晋庆研究的项目就是神经网络,30多年来神经网络的算法并没有改进很多,不过当时用做训练的奔腾计算机主频只有60MHz左右,远不及现在动辄3、4GHz主频的CPU外加GPU。“那时我的DRAM大小只有16MB,用来训练神经网络远远不够,我还是为了买这根内存条花了所有的600块美金积蓄。而现在8GB的DRAM大概只要20到30美金。”

半导体技术突飞猛进的发展,让整个AI产业变化非常大,虽然现在的基本算法和过去基本一样,但在强大的算力和大数据加持下,滕晋庆认为现在用好AI技术能做到很多过去不敢想象的事。“所以大数据分析和人工智能也是Cadence会着重布局的领域,用来增强我们的系统设计和EDA设计能力。”

AI技术的快速发展,同样也带来了一些不可忽视的问题。例如ChatGPT带动AIGC类应用火爆,也带来了对算力的更大需求,不过如今大算力芯片的功耗普遍在300W以上,服务器集群的用电量动辄达到小城市的水平。减碳、降低功耗的同时,保证高性能,无疑是业界面临的最大难题,Cadence这样的公司能够为芯片实现高性能、低功耗做些什么呢?

我们都知道,芯片公司在做设计时最看重的就是PPA(Performance、Power、Area),而对于现在的AI芯片、手机芯片来说,如何用最小的Power(功耗)去达到最好的Performance(性能)显得比以往都重要得多。据悉,Cadence每年都会优化数字设计算法,以把芯片功耗降低10%到15%。

“Cadence这样的EDA公司在减少芯片功耗这件事上,对这个世界贡献很大。我们所做的努力,可以帮全球减少三个核发电厂,因为现在的芯片数量都是以亿计的。” 滕晋庆说到。

其实在芯片降能耗这件事上,分为工艺相关(technology dependent)和工艺无关(technology independent),如果说“工艺无关”主要靠设计端,那么“工艺相关”就需要与晶圆代工紧密合作。

滕晋庆举例道,每种工艺的晶体管长得都不一样,每种的金属厚度、宽度也都不太一样,根据这些不同,EDA公司会开发一些算法让它们达到最优功率。这就是近年来晶圆厂与原厂间最流行的设计工艺协同优化(DTCO,design technology co-optimization)。即便是目前拥有最先进工艺的晶圆厂,都要必须跟EDA厂商合作,让各类工具能够适应其工艺,以达到最好的能效比(performance at power),真正地通过合作把功耗降下来。

而在“工艺无关”的节能方面,Cadence的Joules RTL design studio工具也能在设计端就极大地优化能耗。例如在做RTL级设计时的架构阶段(architecting)就可以进行能耗优化,让前端工程师能很快地得到他们设计PPA的反馈,当前端工程师有了PPA的预估,就可以迅速调整RTL,以达到更小的功耗。

芯片设计工程师对于 EDA 工具的性能需求几乎是无上限的,随着摩尔定律不断逼近极限以及行业对于高性能芯片的极致追求,需要打通设计、封装、PCB 等多领域之间的跨度,来提高芯片的设计效率和性能。但由于多数的设计者只能精通单一领域的设计性能,所以需要 EDA 工具承担起训练设计全职专家的角色来完成整个过程的切分和整合。

拿全世界都在谈的3D-IC来说,中国工程师的热情度是最高的,为此Cadence配合中国市场做了非常多的创新。三年前,Cadence推出了名为Integrity 3D-IC的平台工具,就是为了做3D芯片而生的。

如果是那种PCB板这种封装级别(package level)的 3D-IC,已经不是什么新鲜事,“但我们想要做的是真正的3D-IC,是两个晶圆的堆叠(wafer on wafer),因为只有这样芯片的通信带宽才会变大。”滕晋庆说到。

不过3D-IC这个词在行业中火了几年,但目前来仍然没有实现大面积商用,其中面临最大的挑战有两个:

无论3D-IC,还是近年来很火的Chiplet,芯片结构都在往越来越复杂、紧凑的方向发展。密度增大导致芯片内部热量比传统2D芯片更难散出,不同工艺的晶粒堆栈之间,产生的应力也是千奇百怪。EDA工具要在热分析和应力分析、优化上帮助芯片设计工程师,需要一个非常完整的系统整合。

“不止要包括数字设计、模拟设计、PCB设计、封装,还包括热分析、EMI分析、版图与逻辑(LVS)分析、设计规则(DRC)分析、时序(timing)分析等。” 滕晋庆表示,例如Cadence的Voltus就是用于设计早期的分析工具(ERA,Early Rail Analysis),尤其对于3D-IC这样复杂的芯片,不可能等到两个芯片堆叠起来,到了快要流片时才发现散热不行,需要在早期做大模块布局时就找到问题,如果发现这两个模块堆在一起会过热,就可以及时把它们错开。

工具整合的关键是IHDB(Integrated Hierarchical Database),简单来说,IHDB的作用就是把两个Die堆叠在一起时,Integrity 3D-IC可以基于同一个数据平台去调用各种分析工具,去完成早期分析的工作。

把这些工具整合在一起去做分析,还只是第一步,接下来把这些分析出的结果回归到实施工具后再优化,才是第二步。“Cadence在过去的两年中,在这两步上都有非常大的进展,但正如我刚才所说的,还没有解决(3D-IC)所有的问题。”他说到,“但我认为3D-IC技术已经慢慢成熟,材料如果再进步一点,在中国最晚两三年之内肯定会开花结果。”

汽车电子同样是一个非常新,且未来成长空间最大的领域之一,尤其在中国这个新能源汽车大国,对汽车芯片的需求比世界任何其他地方都要多。

滕晋庆很自豪地表示,现在世界上的顶级车用半导体公司大部分都在用Cadence的工具,“车规芯片有很多规格,需要从验证开始,到实施、签核平台去更有效地去帮助它们达到车规的安全性和可靠性要求。如何用EDA工具帮助车规芯片达到更安全、更可靠、PPA更好,我觉得这才是真正的差异化,而并不是那些规格。”

车用芯片目前有两个大方向,第一是ADAS相关,这类芯片对算力要求非常高,所以对PPA的要求与我们常见的电脑CPU、手机芯片要求差不多。

第二是车规级MCU,这类芯片在功能安全要求上,国内外企业都一样。但是滕晋庆觉得,国内车规芯片厂商与传统车规芯片大厂不一样的地方是,传统大厂历史悠久,通常既有安全工程师部门,也有芯片工程师部门,两者之间沟通很少。“但是这一两年崛起的中国车用芯片公司做得更好,把安全工程师和芯片工程师放在一起工作,达到了更好的效率,对芯片安全性和可靠性也更好。”

他认为,这是中国车规芯片厂商的一大特点。“就好比现在是一群新朋友,聚在一起学习新事物,可以随时彼此沟通,而且接受新事物的速度会更快。”

Cadence为了配合这种芯片设计和安全工程师协同工作,推出了USF标准语言。以前可能芯片工程师讲“ABCD”,安全工程师讲“甲乙丙丁”,现在大家都可以用同一种工作语言、在同一个频道上进行沟通,保证效率。

PPA也是车规芯片企业面临的难题之一。往往在保证安全后,会发现芯片面积变大了很多,本来只需要一个模块能够做完的,现在要用两个模块同时完成同样的功能,才能最后保证信号一致性。

“虽然这样严谨对安全是好的,但芯片面积增大带来的问题是成本变高。” 滕晋庆说到,在这种的情况下,Cadence能做的是努力帮助芯片公司把芯片整体性能提升的同时,也把成本降下来。

AI如今无处不在,也在EDA工具中。在做芯片设计时,工程师往往不知道最优解在哪,所以EDA工具会在很多算法代码里都用上启发式的(heuristic)“假设”,然而这些假设都不一定正确,甚至在不同情况下,这些假设可能都不是对的。怎么破?

可以从大数据分析,去辨别这些启发式假设的正确性,再根据设计做一些调整,从而得到更好的结果。这也是目前AI在EDA工具中最常用的方式。

举例来说,用公式来计算一颗芯片的非线性最优化函数(non-linear optimization function),什么样的结果最好?肯定是希望timing、power和area都达到最优。但要同时达到三个最优的目的,三者又属于完全不一样的单元,所以前面要加一个常量(Constance)去平衡——α乘以timing,加上β乘以power,加上γ乘以area。

“α,β,γ其实就是在做trade-off(权衡)。把α加大一点,就会更强调timing,把β加大一点,会更强调power。可是针对每个设计,α、β、γ应该是不一样的,怎么去解决这个问题?” 滕晋庆解释道,“这时候就可以用AI在数据中进行机器学习,找出对这个设计最好的α、β、γ,通常借助这样的学习,我们可以得到5-10%的芯片PPA表现提升。”

Cadence做这件事情的工具叫做Cerebrus,是一个帮助工程师提高效率、得到最优解的机器学习工具。比如做数字设计,从RTL 到最后GDS一共有十步,每一步里面都要调用三个参数,每个参数有三个选项,算下来是海量的数据,不可能一个一个尝试。可能一个资深工程师亲自做一遍,看看布图规划(floorplan)和结果就知道要调什么参数了,但这都依靠经验。

机器学习的优势是把人的经验放到机器里,Cerebrus学习了这些经验后,可以通过增强型自学习快速地帮工程师找到最好的选择。机器学习已经被证明对于提升PPA很有效,芯片整体PPA提升5-10%并不简单,要知道,即便每次工艺的迭代也只能带来10-20%的提升。

AI用在PCBA设计上,同样也能更大地提升效率。

以往Layout工程师在使用Allegro画图时,面对一块板子上几千个零部件,用纯手工起码要画6个月,因为并不是所有元器件都是形状规则的。如今利用AI去做电路板设计,已经基本上可以实现自动化,来取代很多以前需要纯手工完成的工作。

“这在过去看来是很不可思议的。以前要画6个月,现在只要电脑转一个小时,可能已经完成90%的工作了。” 滕晋庆说到,不过对于AI的崛起是否会令一些工程师失业的问题上,他则表现得很乐观,“我们现在还是缺工程师的。Cadence努力的方向不是让工程师失去工作,而是让现有工程师能够迎接未来更大的挑战。因为芯片变得比以前更复杂了。”

在市场方面,Cadence有一个策略叫“win with winner”,指的是只有与胜者(winner)一同工作才能最终赢得市场。基于这样的理念,Cadence也定义了很多市场上的胜者,并和他们共同进步。由于这些优秀企业做的都是最领先的设计,采用最先进的工艺,作为工具提供者的Cadence也自然而然地实现了成长。这是Cadence的全球性策略,当然也包括中国市场。

EDA行业的发展史,就是一部大型的并购史。Cadence也不例外,自1988年成立以来一直采取激进的收购方式来获取更多的EDA技术,截至目前共计百余家企业纳入Cadence麾下。

近年来,Cadence收购了很多系统级仿真领域的公司,并且还在持续物色并购目标。滕晋庆认为,系统设计是一个巨大而且持续不断发展的市场,加上Cadence在计算软件的优势,“我相信可以在系统设计领域做得非常好。目前整个Cadence员工超过1万人,其中从事系统方面的已超千人。”

此外,Cadence还在研发(R&D)上持续大手笔投入。据介绍,去年公司35%的利润投在研发上,是目前EDA领域排名第一的。拿滕晋庆团队的1900个人来说,其中就有600个是博士。

除了在研发上的投入,Cadence对于公司的内部投资也非常慷慨,在《财富杂志》(Fortune 100)上连续9年被评为Great Places to Work(最佳工作场所),中国区也连续8年得到最佳职场的殊荣。

“我们不只是对客户好,对内部员工也非常照顾,这也是我们的企业文化。” 滕晋庆说到,这几年中国区从700多人增加到了1000多人,未来还会继续加大中国团队的扩充力度。

文章来自:https://www.eet-china.com/